USB 3.x Controller

Mature solution featuring xHCI Host, Device, and Dual-Role The Controller IP for USB 3.1/3.0 offerings include xHCI Host (3.0), D…

Overview

Mature solution featuring xHCI Host, Device, and Dual-Role

The Controller IP for USB 3.1/3.0 offerings include xHCI Host (3.0), Device (3.0/3.1), and Dual-Role Device (3.0/3.1) controllers. USB 3.0 IP from Cadence was one of the first to receive a certification for compliance with the USB 3.0 specification from USB-IF.

Key features

- Full Link Power Management (U0, U1, U2, and U3) with LFPS support

- Up to 15 IN and 15 OUT configurable endpoints

- Power and clock gating feature support

- Multi-channel Scatter/Gather DMA with TRB caching

- AXI features 128-bit datapath width and 64-bit address width

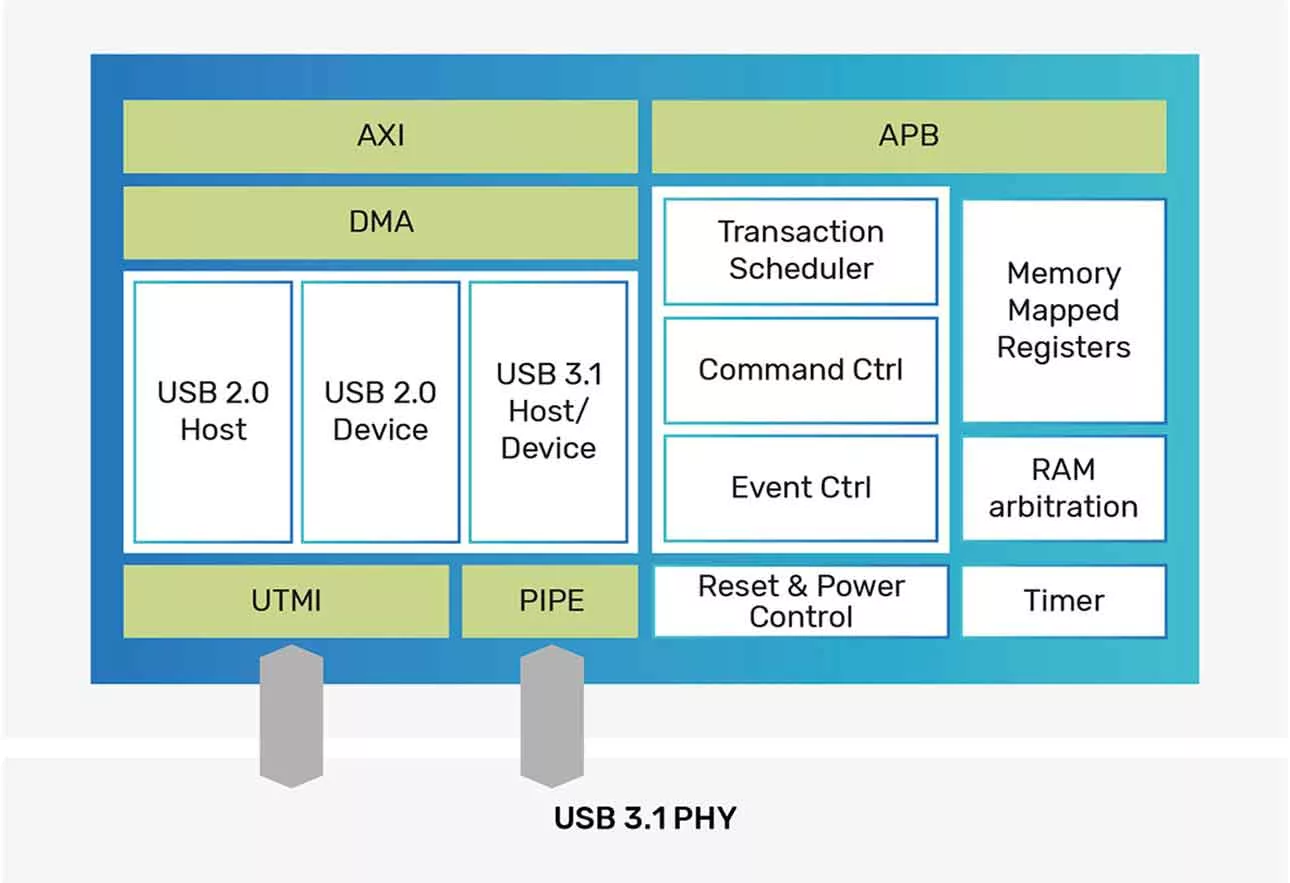

Block Diagram

Applications

- Automotive,

- Communications,

- Consumer Electronics,

- Data Processing,

- Industrial and Medical,

- Military/Civil Aerospace,

- Others

What’s Included?

- Synthesizable RTL

- Testbench

- Synthesis and simulation support files

- Documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is USB 3.x Controller?

USB 3.x Controller is a USB IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.