Provider

Key ASIC was incorporated in the year 2005. In 2006, we were awarded Multimedia Super Corridor (MSC) Status by the Malaysia Digital Economy Corporation (MDEC). We started with the design of IP, ASIC, and SoC. In 2009, we were listed on the main board of KLSE. Khazanah and CIMB are our main investors.

Key ASIC is not only a leading ASIC / SoC design service company, we are also a turnkey service company from spec-in to system module that focuses on AI chips, IoT, and medical applications. We are committed to providing customers with competitive SoC professional one-stop design services in terms of PPA (Performance, Power, and Area).

Based in Kuala Lumpur, Malaysia with R&D Centers in Malaysia and Tai Yuen Hi-Tech Industrial Park Taiwan, Key ASIC provides ODM and OEM of ASIC design services from Specification, RTL, Netlist to silicon, as well as process migration from GDSII.

Our experienced SoC designer and engineers combined with extensive manufacturing, logistics resources, and a flexible engagement model can provide Key ASIC customers with a comprehensive support system for modular ASIC innovation from IP development through prototype to production.

Learn more about Oscillator IP core

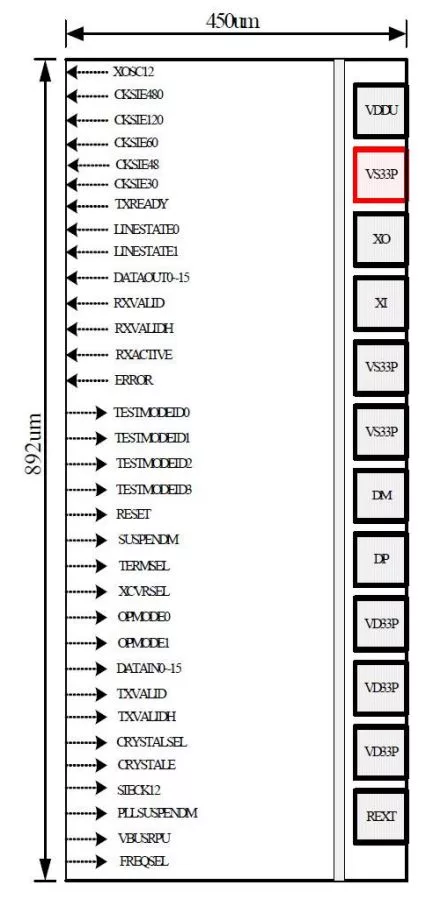

In this paper, we present a flexible ring oscillator IP designed for a 40nm CMOS technology, whose oscillation frequency can be chosen from 200kHz to 20MHz. It was developed using a new design approach, in which analog IPs are designed from scratch to be flexible, employing modular blocks that can be easily customized. The IP is silicon proven. It works with a supply voltage of 1.2V and features 5% frequency accuracy, occupying an area of 0.0022mm2.

This article outlines Key ASIC R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

This article outlines our R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

How do you ensure that every part of a system receives the clock it needs—without wasting power or sacrificing performance? The answer lies in creating a well-structured frequency plan built around a PLL.

Agile Analog’s tamper detection IP is a comprehensive set of sensors and monitors designed to detect a wide variety of physical attacks and side-channel attacks (SCAs). T

Unfortunately, precise thermal monitoring reached an inflection point at 2nm, with traditional solutions proving less practical below 3nm. To tackle the issue, this article delves into a novel approach, accurate to ±1.0°C, that overcomes this critical challenge.