Overview

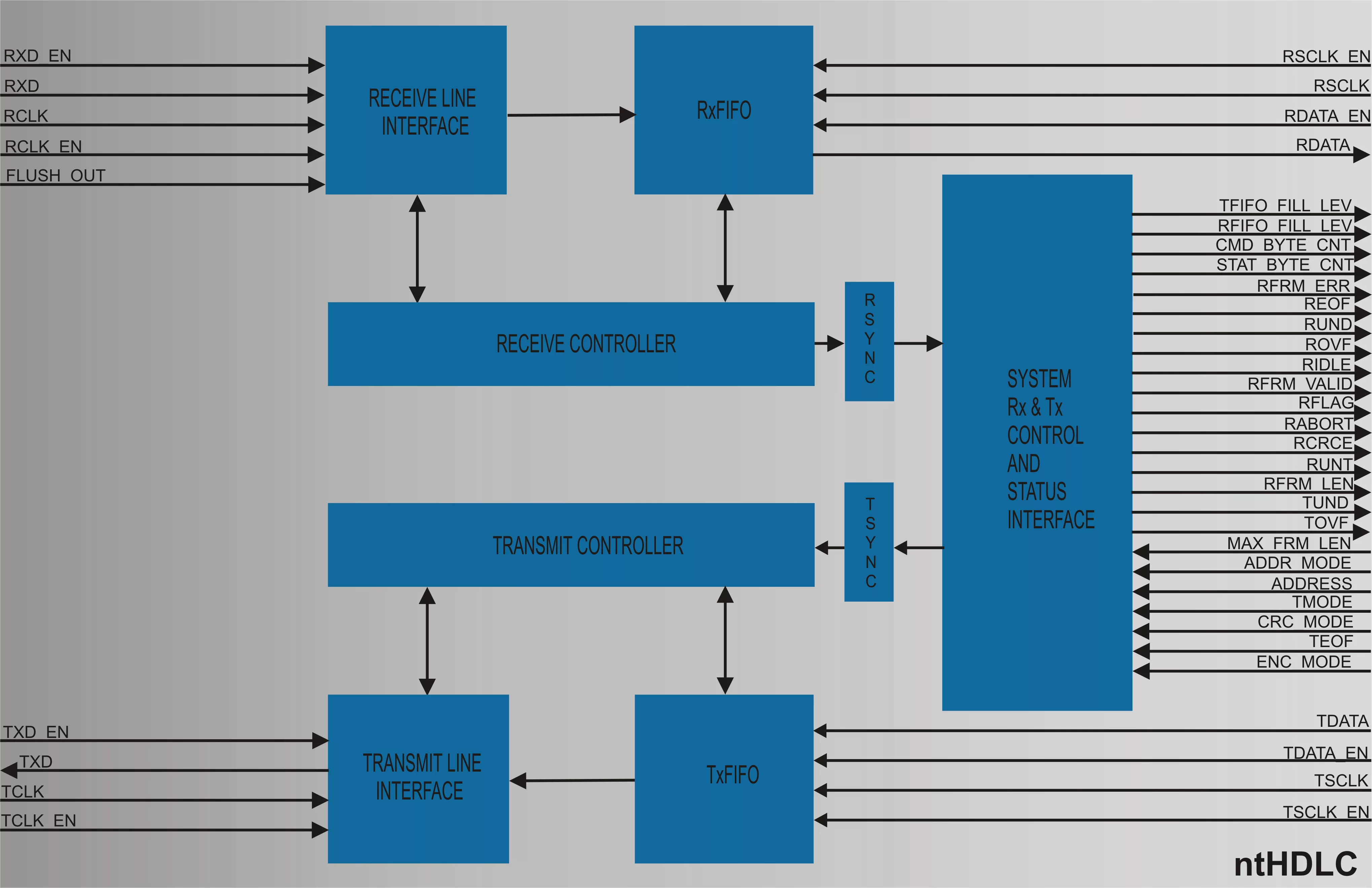

Noesis Technologies ntHDLC single channel High-Level Data Link Controller (HDLC) is a full-duplex transceiver with independent transmit and receive units for synchronous framing bit-level HDLC protocol operations. The ntHDLC can handle interframe and delimiting flags, frame check sequence based on CCITT CRC16/CRC32 polynomial, normal or transparent transmission modes, abort generation and detection. The system interface is very flexible and can be adapted towards FIFO, uP, or DMA controllers. The transmit and receive units and their associated control and status logic are independent. This partitioning strategy enables the Tx and Rx units to be instantiated in different place and/or level of the design hierarchy. Each unit (Tx, Rx and back-end interface) has its own clock domain with synchronous clock enable. Communication between the various clock domains is achieved via synchronization logic blocks.

Learn more about HDLC IP core

One not-so-glamorous but vitally important use for CAST digital IP cores is to replace obsolete parts. Many of our cores can provide the answer if you’re maintaining a legacy system and need to make your own FPGA for a discrete part that was discontinued years ago, or perhaps consolidating a working but ancient board design into a single new chip.

Build safety-critical automotive, aeronautic, space and other systems with the Functional Safety RISC-V Processor IP core from CAST and PolarFire® FPGAs.

D32PRO is one of the newest 32-bit CPUs available on the market. It’s been designed by Digital Core Design, IP Core provider and SoC design house from Poland, responsible e.g. for the world’s fastest or world’s smallest 8051 CPU. DCD launched more than 70 different architectures since 1999, which have been implemented in more than 300 000 000 electronic devices, that’s why one can be sure that quite considerable experience stands behind the D32PRO.

This paper describes a unique approach for developing drivers using hardware abstraction and standard APIs for hardware and software interfaces.

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP