RISC-V IOPMP IP

The I/O Physical Memory Protection (IOPMP) unit is a hardware-based access control mechanism designed to safeguard memory regions…

Overview

The I/O Physical Memory Protection (IOPMP) unit is a hardware-based access control mechanism designed to safeguard memory regions in RISC-V SoCs. It ensures only authorized devices and masters can access sensitive memory areas, enabling secure and reliable system operation.

Key features

- Fully configurable – 28 configurable design parameters enabling optimal trade-offs across area, power, latency and throughput

- Complete feature set – implements all mandatory and optional features

- High-performance design fully pipelined design optimized for high-frequency, singlecycle throughput

- Inline integration model – processes transaction requests and responses directly through the IOPMP

- Flexible addressing – Four address modes, with minimum granularity of 8 bytes Robust protection – triggers interrupts and detailed violation logging

- Outstanding request handling – up to 32 concurrent requests

- Scalable resources – up to 63 MDs

- Customizable RRIDs – up to 64 RRIDs, with flexible mapping to any MD

- Customizable Array entries – up to 128 entries with up to 48 priority entries

- Tapeout ready – verified with a UVM test bench, RAL, and C-reference model, 100% coverage closure

- Technology optimized – synthesized for 12nm/1GHz

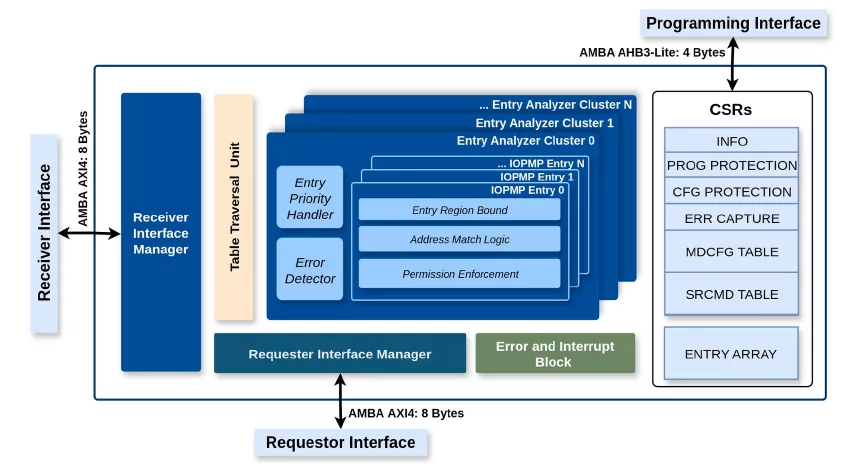

Block Diagram

Benefits

- Fine-Grained Memory Protection - Define multiple memory regions with configurable read, write, and execute permissions.

- Hardware-Enforced Security - Blocks unauthorized DMA and peripheral access before they can compromise system integrity.

- Flexible Configuration - Supports dynamic reconfiguration for multi-tenant or virtualization scenarios.

- Low Latency & Lightweight - Designed to minimize performance overhead while maximizing system resilience.

- RISC-V Standards Aligned - Fully compatible with the latest RISC-V specifications and open hardware ecosystem.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Security Coprocessor IP core

Internal JTAG - A cutting-edge solution for embedded instrument testing in SoC: Part 1

Crypto-RV: High-Efficiency FPGA-Based RISC-V Cryptographic Co-Processor for IoT Security

Security in vehicular systems

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

The Fundamentals of a SHA-256 Master/Slave Authentication System

Frequently asked questions about Security Coprocessor IP cores

What is RISC-V IOPMP IP?

RISC-V IOPMP IP is a Security Coprocessor IP core from 10xEngineers listed on Semi IP Hub.

How should engineers evaluate this Security Coprocessor?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Security Coprocessor IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.