RF Comparator

The TI-RF-CMP is a low power RF comparator with 4 ns propagation delay designed for using in applications, where continuous-into-…

Overview

The TI-RF-CMP is a low power RF comparator with 4 ns propagation delay designed for using in applications, where continuous-into-discrete signal conversion or comparison of voltages is required. The comparator can be used in digital systems for clock recovery. The device is equipped with the latching (fixation) function of the output signal. The input stage cascade is implemented in CMOS transistors providing low input bias current. The comparator operation is specified over the industrial temperature range (-40°C to +85°C).

GDSII database contains a ring of pads with built-in ESD-protection up to 2000 V.

Key features

- Single-supply operation: 3 V to 5 V

- 4 ns propagation delay at 5 V supply voltage

- Up to 150 MHz input

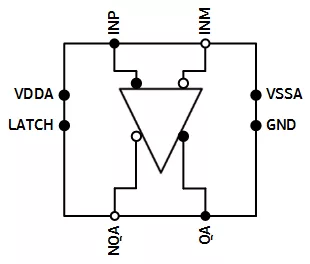

Block Diagram

Benefits

- Low input bias current

- Latch function

- ESD-protection

Applications

- High-speed ADC’s

- Digital communications

- Clock recovery and clock distribution

- Phase detectors

- High speed sampling

- Zero-crossing detector

What’s Included?

- Datasheet

- GDSII database

- Customer support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Comparator IP core

Achieving Groundbreaking Performance with a Digital PLL

Improving Battery-Powered Device Operation Time Thanks To Power Efficient Sleep Mode

Generating High Speed CSI2 Video by an FPGA

Design & Verify Virtual Platform with reusable TLM 2.0

Metric Driven Verification of Reconfigurable Memory Controller IPs Using UVM Methodology for Improved Verification Effectiveness and Reusability

Frequently asked questions about Comparator IP cores

What is RF Comparator?

RF Comparator is a Comparator IP core from Thesys-Intechna listed on Semi IP Hub.

How should engineers evaluate this Comparator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Comparator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.