Reed Solomon Decoder IP Core

This high performance, fully programmable Reed Solomon Decoder IP Core is intended for use in a wide range of applications requir…

Overview

This high performance, fully programmable Reed Solomon Decoder IP Core is intended for use in a wide range of applications requiring forward error correction and can be targeted in any ASIC or FPGA technologies.

In channel coding redundancy is inserted in the transmitted information bit-stream. This redundant information is used in the decoder to eliminate the channel noise. The error correction capability of a FEC system is strongly depended on the amount of redundancy as well as on the coding algorithm itself. The Reed Solomon decoder receives an N symbol codeword consisting of a K symbol information block appended with 2T parity symbols, locates and corrects up to T possible symbol errors or up to 2T erasure errors anywhere in the codeword. If more than T symbol errors or 2T erasure errors are received then the decoder marks the codeword as uncorrectable.

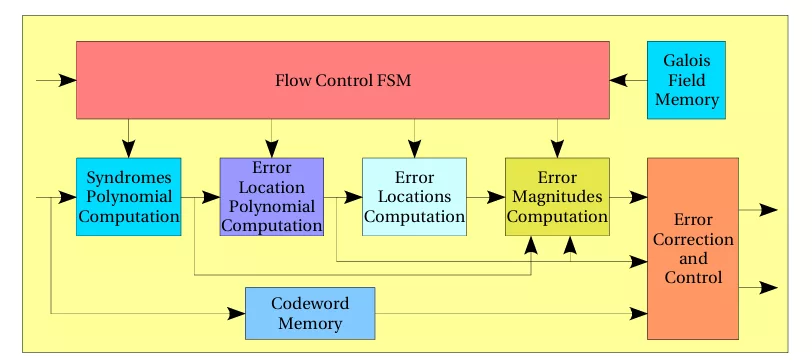

ARCHITECTURE

The decoder is parameterized in terms of bits per symbol (2M), maximum codeword length (N) and maximum correction power (T). It also supports shortened codes by varying on the fly the NVAL and TVAL inputs. Therefore any desirable code-rate can be easily achieved rendering the decoder ideal for adaptive FEC applications. If NVAL=2M-1 then the code is non shortened. If NVAL is less than 2M-1 then the code is shortened. The effective code rate is NVAL / (NVAL-2TVAL). The implementation is very low latency, high speed with a simple interface for applications.

Key features

- Continuous, very high-speed, time-domain Reed-Solomon decoding algorithm.

- Supports different Reed-Solomon coding standards.

- Code rate can be dynamically varied

- Parameterizable bits per symbol (M).

- Programmable codeword length (NVAL) with parameterizable maximum value (N).

- Programmable number of errors (TVAL) with parameterizable maximum value (T).

- Shortened codes supported (NVAL,TVAL).

- User configured primitive field polynomial.

- User configured generator polynomial.

- Synchronous design.

- Predictable decoder latency.

- Status and performance monitoring signals

Block Diagram

Benefits

- Flexible

- Compact

- Cost-effective

What’s Included?

- Verilog Source Code

- Test Bench

- Sample Syntheis scripts

- Dcumentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is Reed Solomon Decoder IP Core?

Reed Solomon Decoder IP Core is a Channel Coding IP core from ASICS World Services, LTD. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.