Vendor:

Xiphera Ltd

Category:

Random Number Generator

Pseudo Random Number Generator, high-speed version (AES256_CTR_DRBG)

XIP8103H from Xiphera is a Pseudorandom Number Generator (PRNG) Intellectual Property (IP) core.

Overview

XIP8103H from Xiphera is a Pseudorandom Number Generator (PRNG) Intellectual Property (IP) core. XIP8103H is based on Counter (CTR) operation mode of a 256-bit Advanced Encryption Standard (AES) and uses a high-speed AES-CTR implementation as an integral building block.

XIP8103H has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology, and the functionality of XIP8103H does not rely on any FPGA manufacturer-specific features.

XIP8103H has also been successfully validated in the CAVP (Cryptographic Algorithm Validation Program) by NIST (National Institute for Standards and Technology).

XIP8103H has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology, and the functionality of XIP8103H does not rely on any FPGA manufacturer-specific features.

XIP8103H has also been successfully validated in the CAVP (Cryptographic Algorithm Validation Program) by NIST (National Institute for Standards and Technology).

Key features

- High Performance: XIP8103H can achieve over 69 Gbps throughput, while consuming only about 18000 Lookup Tables (LUTs) in a typical FPGA implementation.

- Versatility: XIP8103B supports the forward prediction resistance mode, which can be set on and off between output generation, as well as the use of personalization strings and additional inputs for instantiation and reseeding.

- Standard Compliance: XIP8103B is compliant with the NIST SP800-90A specification.

- XIP8103B can be combined with Xiphera’s NIST SP800-90Bcompliant XIP8001B to form a NIST SP800-90C compliant Random Bit Generator (RBG).

- Easy integration with AXI4-lite and AXI stream interfaces.

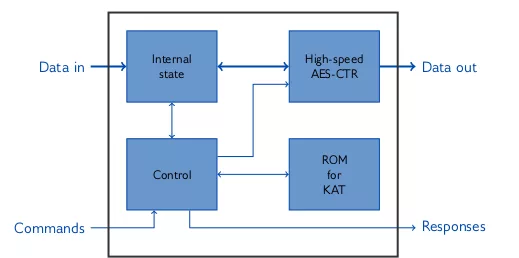

Block Diagram

XIP8103H block diagram

Benefits

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

- Easy to integrate

- Several bus interfaces available

- IP core designed in-house at Xiphera

- Technical support by the original designers and cryptographic experts

- CAVP validated

Applications

- The main functionality of XIP8103H is to produce pseudorandom numbers. Pseudorandom numbers are numbers which look completely random but which are generated deterministically from a seed If the PRNG is properly seeded with a full-entropy seed (like XIP8001B TRNG) its outputs provide as much randomness, or security, as the seed it was seeded with.

What’s Included?

- Please Xiphera for pricing and your preferred delivery method.

- XIP8103H can be shipped in a number of formats, including netlist,

- source code, or encrypted source code.

- Additionally, synthesis scripts, a comprehensive testbench, and a detailed datasheet including an integration guide are included.

Specifications

Identity

Part Number

XIP8103H

Vendor

Xiphera Ltd

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

Xiphera Ltd

HQ:

Finland

Xiphera, Ltd, based in Finland, designs and implements proven cryptographic security for embedded systems. Our strong cryptographic expertise and extensive experience in digital system design enable us to help our customers to protect their most valuable assets.

We offer secure and highly optimised cryptographic Intellectual Property (IP) cores, designed directly for Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs) without software components. Our broad, fully in-house designed, and up-to-date portfolio, including implementations of Post-Quantum Cryptography, enables cost-effective development projects with fast time-to-market – providing peace of mind in a dangerous world.

Learn more about Random Number Generator IP core

How random is random?

Brian Bailey

The Silent Guardian of AI Compute - PUFrt Unifies Hardware Security and Memory Repair to Build the Trust Foundation for AI Factories

At the scale of the Vera Rubin platform, yield, calibration, and security failures compound across tens of thousands of devices. A single unified hardware anchor at the silicon level is not optional, it is architectural necessity. A physical unclonable function-based hardware root-of-trust, PUFrt, jointly developed by eMemory and PUFsecurity, was designed precisely for this role: a fully integrated implementation of the Caliptra 2.0 open standard that simultaneously manages cross-die memory repair and hardware root of trust across the full platform.

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

This article provides an in-depth analysis of the specific PPA challenges introduced by PQC and elucidates how PUF-PQC leverages its unique dualtrack strategy to deliver a robust and flexible Hardware Root of Trust (HRoT) across diverse application scenarios. Furthermore, it demonstrates the integration of Physical Unclonable Function (PUF) with a NIST SP 800-90B compliant True Random Number Generator (TRNG) to serve as critical components of PUFrt (Root of Trust), ensuring the security of post-quantum key generation starting from the entropy source.

X100 - Securing the System - RISC-V AI at the Edge

For years, SiFive has been delivering a range of security capabilities that are optimized for deployment throughout the system, tightly coupled to products from its broad portfolio of processors. Building on the prior blogs that centered on performance and effective coupling of accelerators, I wanted to focus this blog on security and its role in the growing popularity of the SiFive Intelligence X100 product family.

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

A Root of Trust is the foundation on which all secure operations of a computing system depend. It contains the keys used for cryptographic functions and enables a system-wide secure boot process. It is inherently trusted and therefore must be secure by design.

Frequently asked questions about Random Number Generator IP cores

What is Pseudo Random Number Generator, high-speed version (AES256_CTR_DRBG)?

Pseudo Random Number Generator, high-speed version (AES256_CTR_DRBG) is a Random Number Generator IP core from Xiphera Ltd listed on Semi IP Hub.

How should engineers evaluate this Random Number Generator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Random Number Generator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.