PCIe Switch for USB4

The PCIe Switch for USB4 (formerly XpressSWITCH) is a customizable, embedded switch for PCI Express (PCIe) designed for implement…

Overview

The PCIe Switch for USB4 (formerly XpressSWITCH) is a customizable, embedded switch for PCI Express (PCIe) designed for implementations in USB4 devices.

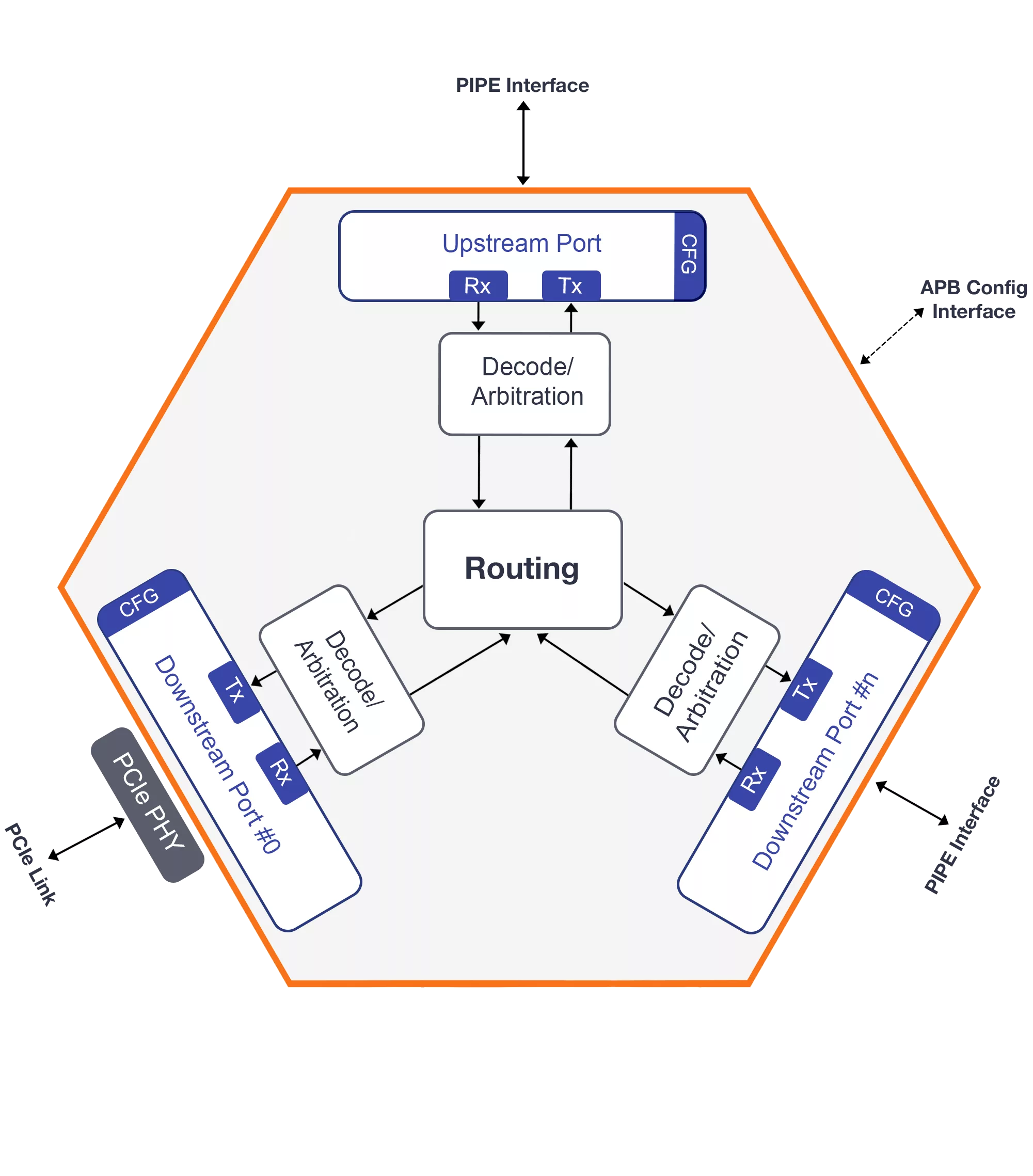

How the PCIe Switch for USB4 Works

A fully configurable fanout switch, the PCIe Switch for USB4 provides one upstream port and up to 31 downstream ports. It enables designers to support tunneling of PCIe traffic in USB4 Hubs as mandated by the USB4 specification, and is also an ideal addition to USB4 Devices or Hosts for attaching internal or external PCIe devices.

By implementing internal PCIe devices, designers can differentiate their USB4 ICs while reducing latency and power consumption. The PCIe Switch for USB4 provides a flexible, scalable and configurable PCIe switching solution for USB4 Hubs, Hosts and Devices.

Key features

- PCI Express Interfaces (upstream and downstream ports)

- Designed to the USB4 Specification v1.0

- Follows PCIe 1.0 protocol, but can operate at any compatible speed

- 1 upstream port, up to 31 downstream ports

- Supports PCIe Base Revision 5.0, backward compatible down to 3.1

- Supports PHY Interface for PCIe (PIPE) 5.x

- Single Virtual Channel (VC) implementation

- Configurable PIPE interface (8-bit, 16-bit, 32-bit, 64-bit)

- Configurable Receive and Replay buffer sizes

- Advanced Error Reporting (AER) supported on each port

- ECRC generation and check

- LTR, ACS, FPB, PTM, Hot Plug enabled per USB4 Specification mandate for Hubs

- Lane reversal supported

- Switch upstream port supports multiple physical functions

- Supports for in-the-flow processing

- ASPM L1, L2

- Clock and Power gating

- Peer-to-peer communication between downstream ports

- Switching Logic

- PCIe TLP routing: Configuration, Memory Write/Read, I/O and Messages Packets

- L1 and wake-up events forwarding

- Peer-to-Peer transactions support between downstream ports

- Broadcast and Multicast supported

- Downstream Port Containment (DPC and eDPC) supported

- Round-Robin arbitration

- No Packet buffering (cut-through architecture) for reduced latency

- Built-in advanced data protection including ECRC, LCRC, ECC and Parity

- Test port available for switch logic monitoring

- Integrated Clock Domain Crossing to support user-specified frequency in the Switching logic

Block Diagram

Benefits

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)

- Architecture allows insertion of custom processing in-the-flow (i.e. filtering, encryption, etc.)

- The only solution that supports Hot Plug

Applications

- HPC,

- Cloud Computing,

- AI,

- Machine Learning,

- Enterprise,

- Networking,

- Automotive,

- AR/VR,

- Test and Measurement

What’s Included?

- IP files

- Verilog RTL source code

- Libraries for functional simulation

- Configuration assistant GUI (Wizard)

- Verification Environment

- Documentation

- Reference Design

- Synthesizable Verilog RTL source code

- Simulation environment and test scripts

- Synthesis project & constraint files

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about PCI Express IP core

Realizing the Performance Potential of a PCI-Express IP

Navigating the Complexity of Address Translation Verification in PCI Express 6.0

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Frequently asked questions about PCIe IP cores

What is PCIe Switch for USB4?

PCIe Switch for USB4 is a PCI Express IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.