PCIe 2.1 Controller with AXI

The PCIe 2.1 Controller (formerly XpressRICH) is designed to achieve maximum PCI Express (PCIe) 2.1 performance with great design…

Overview

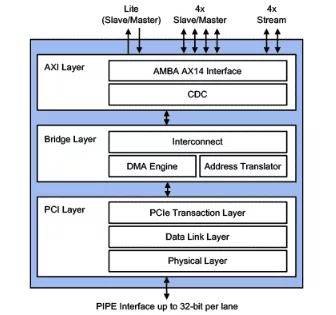

The PCIe 2.1 Controller (formerly XpressRICH) is designed to achieve maximum PCI Express (PCIe) 2.1 performance with great design flexibility and ease of integration. It is backward compatible with the PCIe 1.1 specification. A PCIe 2.1 Controller with AXI (formerly XpressRICH-AXI) is also available. The controller delivers high-bandwidth and low-latency connectivity for demanding applications in data center, edge and graphics.

How the PCIe 2.1 Controller Works

The PCIe 2.1 Controller is configurable and scalable IP designed for ASIC and FPGA implementation. It supports the PCIe 2.1/1.1 specifications, as well as the PHY Interface for PCI Express (PIPE) specification. The IP can be configured to support endpoint, root port, switch port, and dual-mode topologies, allowing for a variety of use models.

The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters, including data path size, PIPE interface width, low power support, SR-IOV, ECC, AER, etc. for optimal throughput, latency, size and power. The PCIe 2.1 Controller is verified using multiple PCIe VIPs and test suites, and is silicon proven in hundreds of designs in production.

Key features

- PCI Express layer

- Compliant with the PCI Express 2.1/1.1, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 5 GT/s and 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

- AMBA AXI layer

- Compliant with the AMBA® AXI™ Protocol Specification (AXI3, AXI4 and AXI4-Lite) and AMBA® 4 AXI4-Stream Protocol Specification

- Supports multiple, user-selectable AXI interfaces including AXI Master, AXI Slave, AXI Stream

- Each AXI interface data width independently configurable in 512-, 256-, 128-, and 64-bit

- Each AXI interface can operate in a separate clock domain

- Data engines

- Built-in Legacy DMA engine

- Up to 8 DMA channels, Scatter-Gather, descriptor prefetch

- Completion reordering, interrupt and descriptor reporting

- Optional Address Translation tables for direct PCIe to AXI and AXI to PCIe communication

- Built-in Legacy DMA engine

Block Diagram

Benefits

- 20+ years of experience in design of IP cores for ASIC with specialization in high-speed interface protocols and technologies, more than 6200 customers , including several hundred of ASIC tape-outs

- Silicon target 16 nm FinFET TSMC and 28 nm roadmap

- Configurable user interface with clock-domain-crossing provides maximum interfacing flexibility and throughput.

- Engineered for both ASIC/SoC and FPGA implementations. Allows seamless migration from FPGA prototyping design to ASIC/SoC production design with same RTL. Fully timing closed on leading edge FPGA from Altera and Xilinx.

- Advanced AMBA AXI interconnect enables heterogeneous SoC interfacing. Allows AXI3 and AXI4 peripherals to coexist and communicate efficiently through the interconnect interface.

- Fully configurable communication engine features programmable DMA and Address Translation Windows, allowing flexible and high-performance AXI-to-PCIe, PCIe-to-AXI, and AXI-to-AXI data transfers.

- Smart ordering rules management enables hazards and deadlocks prevention while ensuring optimized traffic flow.

- Configurable error detection and reporting enables application specific error management thus simplifying application software.

- Support for advanced Low Power states enables lower power consumption in energy-conscious applications

- Flexible PCIe interface configuration in endpoint and root port modes. Includes ECAM support for dynamic configuration of the entire PCIe hierarchy from the AXI domain.

- Provided with latency optimized Linux x64 PCIe device driver allowing immediate software development. Driver source code available for custom developments.

Applications

- HPC,

- Cloud Computing,

- AI,

- Machine Learning,

- Enterprise,

- Networking,

- Automotive,

- AR/VR,

- Test and Measurement

What’s Included?

- Verilog RTL,

- Supporting Documentation

Specifications

Identity

Standards & Interfaces

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about PCI Express IP core

Realizing the Performance Potential of a PCI-Express IP

Navigating the Complexity of Address Translation Verification in PCI Express 6.0

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Frequently asked questions about PCIe IP cores

What is PCIe 2.1 Controller with AXI?

PCIe 2.1 Controller with AXI is a PCI Express IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.