NVM OTP XBC TSMC N5 1.2V

Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs.

Overview

Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs. Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges. Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries.

Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7. Synopsys OTP in TSMC N5A is Grade-1 qualified to AEC-Q100 standard

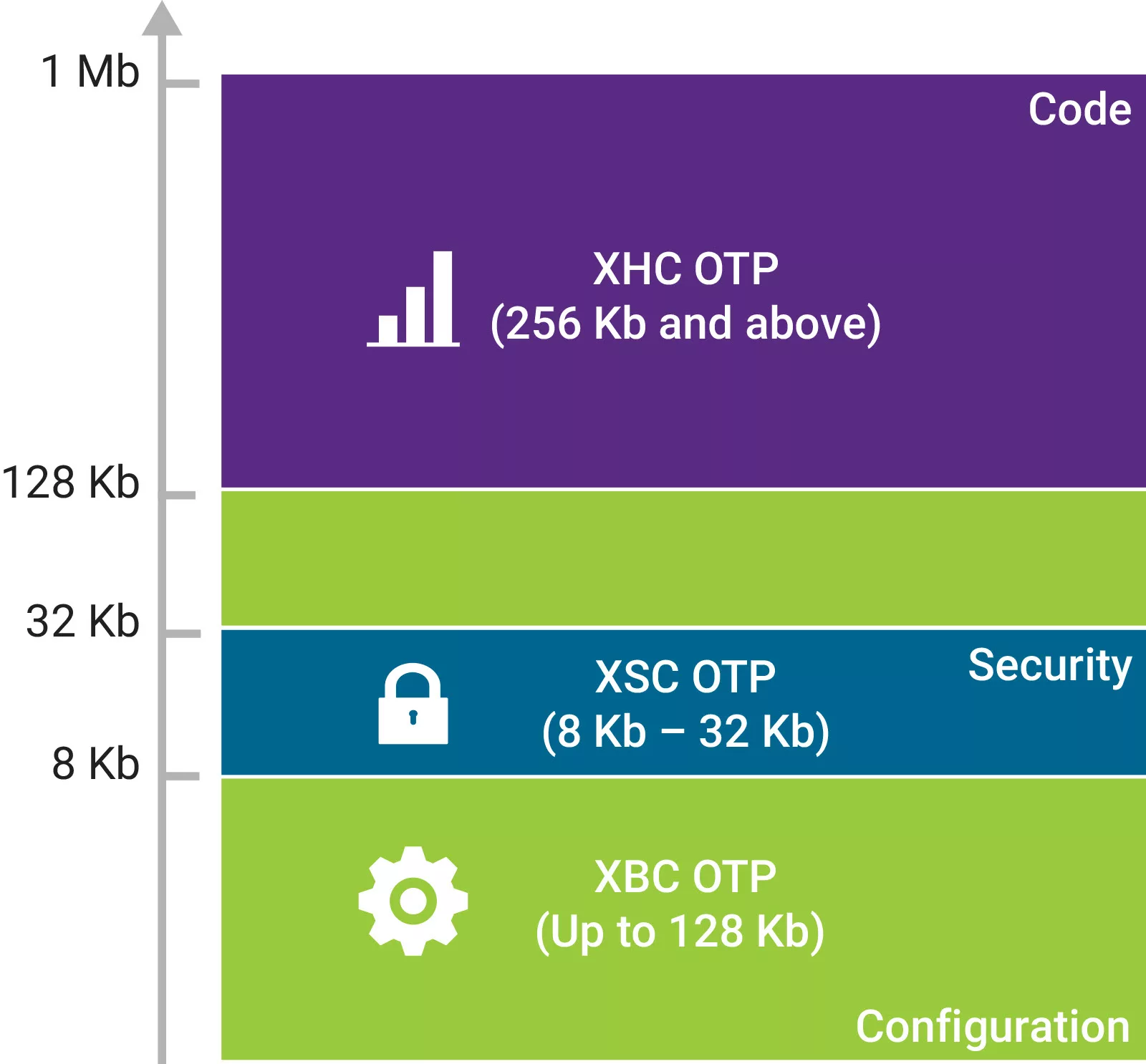

Synopsys OTP NVM offers non-volatile storage for configuration, trimming, calibration, and encryption keys with the Base Capacity OTP product (XBC OTP), code storage with the High-Capacity OTP product (XHC OTP), and secure storage with the Secure Code OTP product (XSC OTP).

Synopsys OTP XBC IP is Automotive Grade 1 AEC-Q100 Qualified and is delivered with ISO 26262 functional safety deliverables for random hardware faults, reducing risk, accelerating AEC-Q100 product-level qualification, and meeting the stringent quality requirements for automotive SoCs.

Synopsys OTP NVM IP

Available in standard CMOS processes, Synopsys OTP IP does not require any additional mask layers or process steps and provides an alternative to mask ROM, eFuse and embedded Flash memory.

Synopsys OTP NVM IP addresses the power, form factor and security requirements of a broad range of applications, including code storage, encryption keys, analog trimming, and IC configuration in Power Management ICs (PMICs), Sensors, Home Entertainment, Automotive, Industrial, Mobile, Mil/Aero and IoT products.

Key features

- Anti-fuse OTP ensure security, scalability, and reliability

- Automotive AEC-Q100 Grade-1 qualified and with ISO 26262 functional safety deliverables for random hardware faults

- Optimized for area, programming time, and power

- High level of security prohibits memory content modification

- Flexible, field-programmable memory

- Built-in error correction schemes available

- Comprehensive manufacturing built-in test features available

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about eFuse / OTP IP core

Optimizing Sensor Performance with 1T-OTP Trimming

Solving Chip Security's Weakest Link

Securing Smart Connected Homes with OTP NVM

Optimal OTP for Advanced Node and Emerging Applications

I-fuse: Most Reliable and Fully Testable OTP

Frequently asked questions about eFuse / OTP IP cores

What is NVM OTP XBC TSMC N5 1.2V?

NVM OTP XBC TSMC N5 1.2V is a eFuse / OTP IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this eFuse / OTP?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this eFuse / OTP IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.