Overview

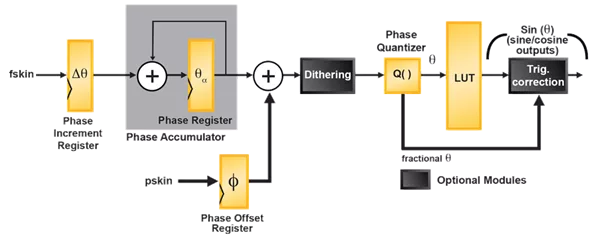

Numerically Controlled Oscillators (NCO), also called Direct Digital Synthesizers (DDS), offer several advantages over other types of oscillators in terms of accuracy, stability and reliability. NCOs provide a flexible architecture that enables easy programmability such as on-the-fly frequency/phase. NCOs are used in many communications systems including digital up/down converters used in 3G wireless and software radio systems, digital PLLs, radar systems, drivers for optical or acoustic transmissions, and multilevel FSK/PSK modulators/demodulators.

Lattice provides a parameterizable NCO IP core that supports multiple channels and a Quadrature Amplitude Modulation (QAM) mode, in addition to other usual configurations. The resource utilization and performance trade-off can be tuned by configuring different parameters of the IP core to obtain the optimal Spurious Free Dynamic Range (SFDR) result. The Lattice NCO core offers a variety of memory reduction schemes and mechanisms for SFDR improvement.

Learn more about Oscillator IP core

In this paper, we present a flexible ring oscillator IP designed for a 40nm CMOS technology, whose oscillation frequency can be chosen from 200kHz to 20MHz. It was developed using a new design approach, in which analog IPs are designed from scratch to be flexible, employing modular blocks that can be easily customized. The IP is silicon proven. It works with a supply voltage of 1.2V and features 5% frequency accuracy, occupying an area of 0.0022mm2.

This article outlines Key ASIC R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

This article outlines our R&D team's upcoming PLL suitable for high-speed SerDes having ultra low jitter with LC- tank VCO, and supporting up to 16 GHz output clock to sample the data.

How do you ensure that every part of a system receives the clock it needs—without wasting power or sacrificing performance? The answer lies in creating a well-structured frequency plan built around a PLL.

Agile Analog’s tamper detection IP is a comprehensive set of sensors and monitors designed to detect a wide variety of physical attacks and side-channel attacks (SCAs). T

Unfortunately, precise thermal monitoring reached an inflection point at 2nm, with traditional solutions proving less practical below 3nm. To tackle the issue, this article delves into a novel approach, accurate to ±1.0°C, that overcomes this critical challenge.