N-channel Multiplexed FIR Filter

FIR_NTAP_MUX is an N-channel multiplexed FIR filter designed for high sample rate applications where hardware resources are limit…

Overview

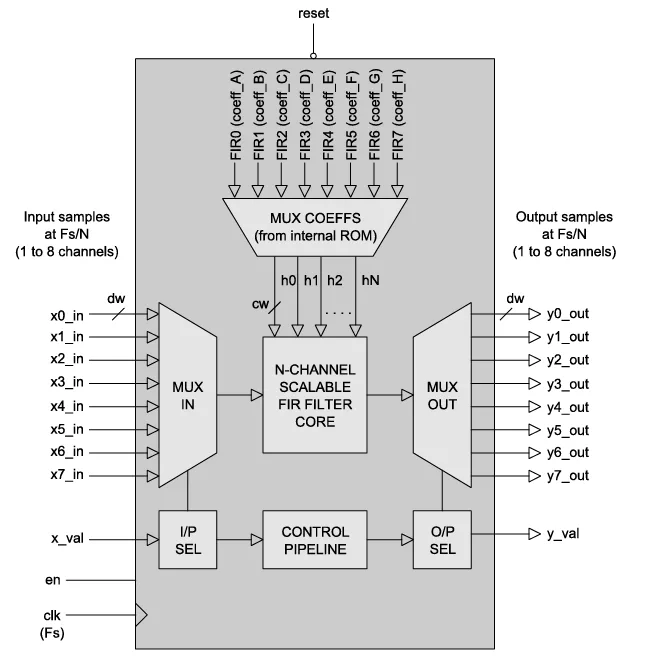

FIR_NTAP_MUX is an N-channel multiplexed FIR filter designed for high sample rate applications where hardware resources are limited. The main filter core is organized as a scalable systolic array permitting the user to specify large order filters without compromising maximum attainable clock-speed.

Essentially the filter functions as if it were 'N' separate FIR filters. Each input sample is multiplexed into the filter at a sample rate equal to FS/N, where FS is the sampling frequency of the main filter core. Likewise, output samples are updated at a frequency of FS/N.

The first sample into the filter is aligned by asserting the signal x_val high. The signal y_val is asserted with the first valid output sample. Data samples are advanced in the pipeline on the rising clock-edge of clk when en is active high. When en is low then all data samples are stalled. The clock-enable signal may be used to temporarily disable the filter - or possibly to modify the effective sampling frequency of the system clock. If the clock-enable is not needed it is recommended that this signal be tied high as it will improve overall circuit performance.

Key features

- Synthesizable, technology independent VHDL Core

- N-channel FIR filter core implemented as a systolic array for speed and scalability

- Support for one or more independent channels (8 maximum)

- Configurable and independent coefficient sets for each channel

- Configurable data width and number of taps

- Symmetric arithmetic rounding limits DC-bias problems

- Output saturation or wrap modes

- Much cheaper than implementing separate FIR filters in parallel as hardware resources are shared between all channels

- Supports 550 MHz+ sample rates (550/N MHz per channel)

Block Diagram

Applications

- High-speed filtering applications where hardware resources are limited - e.g. when it becomes impractical to use multiple FIR filters in parallel

- Dual-channel inputs such as complex valued I/Q in digital communications systems

- Parallel DSP processor architectures

- General purpose FIR filters with odd or even numbers of taps

- Filters with arbitrary sets of coefficients (e.g. non-symmetrical)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is N-channel Multiplexed FIR Filter?

N-channel Multiplexed FIR Filter is a Filters Transforms IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.