Overview

The Atria Logic AL-MPEG2E-SW is a software-based, low power MPEG-2 Main Profile video encoder IP core, targeted for mobile and non-mobile, low power devices in industrial and medical applications. Industrial applications include broadcast contribution portable video recorders and train/bus/truck/airplane black box recorders. Medical applications include operating theater recorders, as well as PACS video archiving.

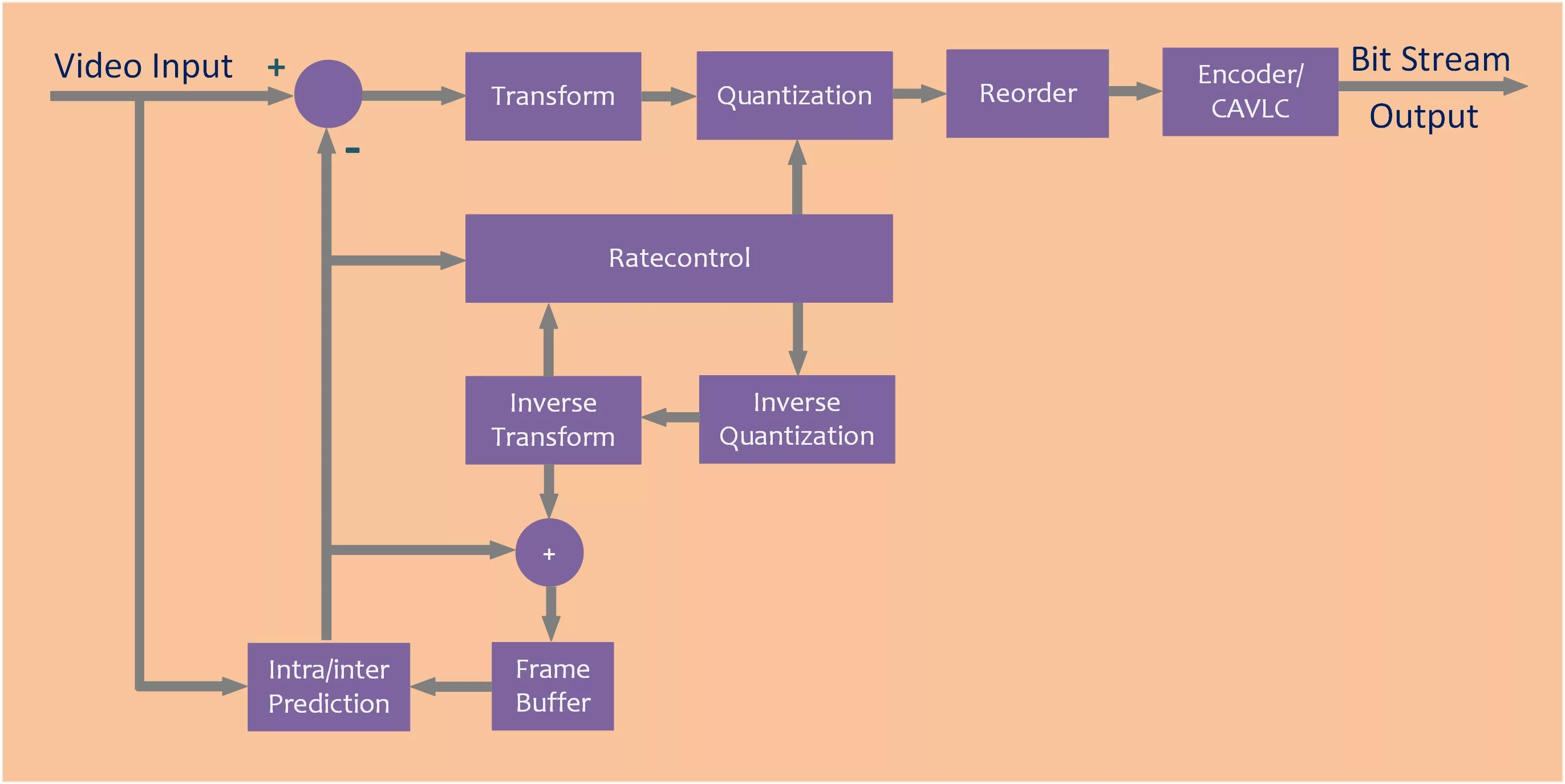

The encoder supports MPEG-2 Main Profile at Low and Main Level IPB encoding up to SD resolutions, and supports both single-pass variable bit rate (VBR) and constant bit rate (CBR) encoding. Support for rate distortion optimization for mode decisions provides exceptional video quality at low bit rates. The encoder is fully MPEG-2 standards compliant.

The implementation includes power-optimizing algorithms that enable the encoder to run at very low power in a Linux or MS Windows environment on a wide range of ARM processors, such as ARM7, ARM9, ARM9E and ARM11, as well as on the EZchip Tilera TilePro64 processors.

Provider

Atria Logic, Inc.

HQ:

USA

Atria Logic is a leading provider of HW/SW FPGA and SoC IP cores and design engineering services, specializing in applications for medical imaging, multimedia, storage and networking. In addition, we also specialize in heterogeneous computing engineering services for computer vision applications in such applications as industrial automation, video surveillance and automotive.

Our IP core portfolio includes H.264 video encoders and decoders, H.264 players, DDR I/II/III and QDR IV Extreme Performance PHY and memory controllers, USB 2/3 controllers, PCIe Gen 1/2 PHYs, NVMe validation test suites, and Gb Ethernet MAC controllers. Our IP cores have been designed for ease of reuse and configurability to speed up SoC and FPGA implementations.

Our design services include IP customization, SoC integration, FPGA and SoC implementations, firmware development, software porting and optimization.

We are headquartered in Sunnyvale, California, USA, in the heart of Silicon Valley.

Technology Focus:

Video/Image processing

Heterogeneous Processing

High Power Computing

Computer Vision and Video Analytics

High speed memory controllers and Standard bus architectures

Network Processing

FPGA/ASIC/SoC design services

HW/SW domain consultancy and services

Business Domains

Medical Imaging

Video Surveillance

Industrial Automation

Enterprise and Datacenter Storage

Broadcast

Automotive Assisted Driver Assistance Systems

Learn more about Video Processing IP core

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

Configurable Processors for Video Processing SOCs

Programmable FPGA devices are the perfect choice for interfacing with multiple high-resolution image sensors simultaneously...

A look at the design of multiprocessor systems-on-chips (MPSoCs) for video applications and how to optimize them for computational power and real-time performance as well as flexibility. Part 1: Architectural approaches to video processing

Building a high-performance, quad-channel H.264 encoder using low-cost, low-power FPGA architecture.

Adding to its growing portfolio of licensable silicon IP subsystems, ARC has announced five configurable video processing subsystems. The subsystems range from the smallest-size AV 402V to the highest-performance AV 417V, and support multi-standard video encoding and decoding at resolutions ranging from CIF to D1.