ITU G.704 E1 Framer/Deframer

Noesis Technologies ntE1_G704 Framer/Deframer is designed for E1 networks and is compliant with ITU recommendations G.704, G.706,…

Overview

Noesis Technologies ntE1_G704 Framer/Deframer is designed for E1 networks and is compliant with ITU recommendations G.704, G.706, G.732, G.775 and O.163. The core provides all the necessary data formatting transforms for transmission over an E1 carrier. E1 is one of the two most widely used TDM (time division multiplexing) carriers incorporating 32 channels, each with a

bandwidth of 64 kbps providing a total bit rate of 2048 kbps.

The ntE1_G704 IP core provides a flexible interface supporting hardware and microprocessor modes. Specifically the core can be connected to a host system either through an 8-bit parallel microprocessor interface (HP mode) or through a set of I/O ports (HW mode). When in HP mode, the microprocessor configures and monitors the functionality of the core through a rich set of registers. When in HW mode, the core is directly controlled and monitored through a set of dedicated ports and no microprocessor control is necessary.

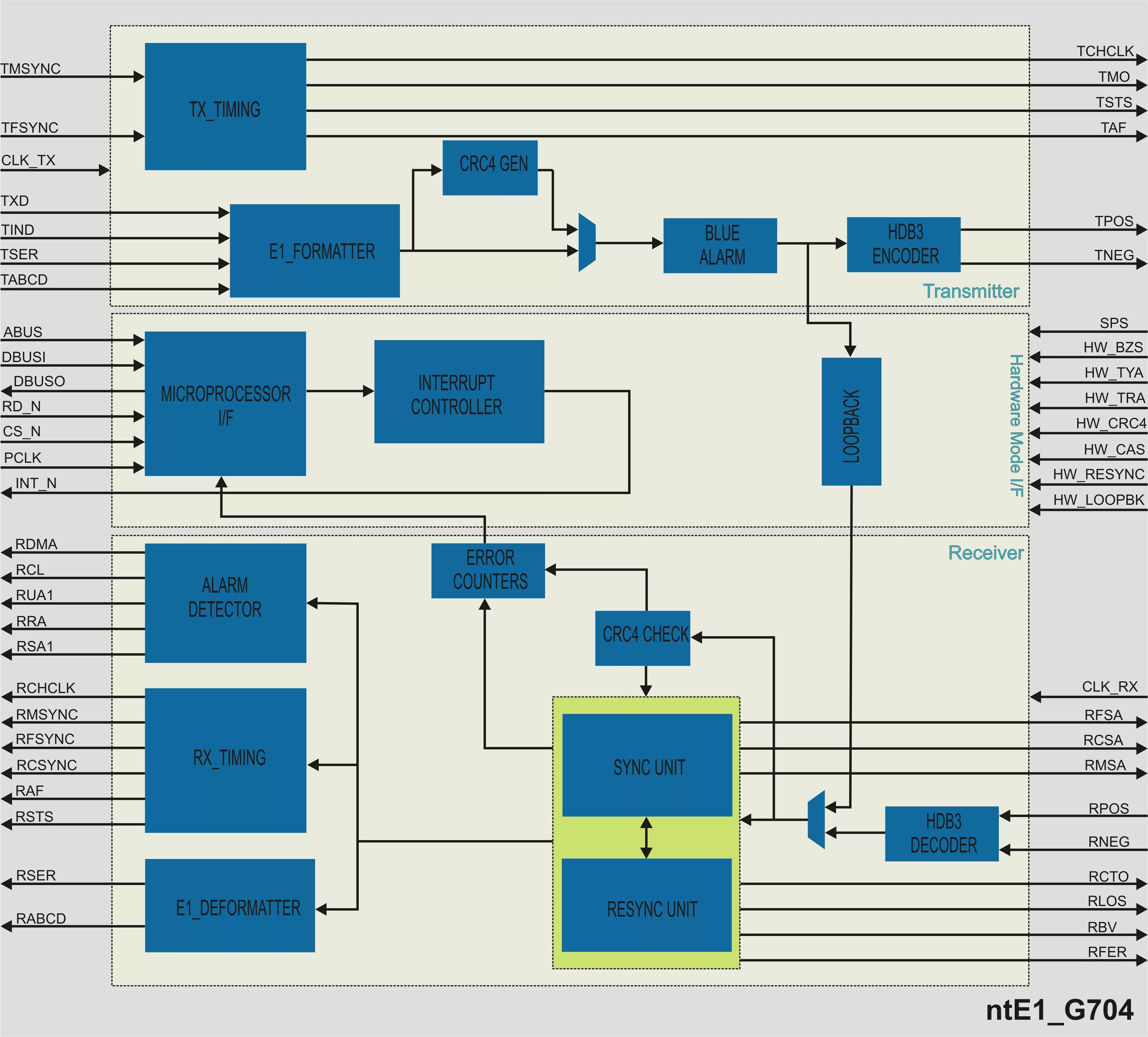

At the transmit side, the framer generates framing patterns, CRC4 bits, formats outgoing and signalling data, generates alarms and clock outputs for data conditioning and decoding. At the receive side, the deframer establishes frame / multiframe synchronization, extracts data, signalling and alarm flags. It provides information like frame, multiframe alignment, calculates CRC4, counts CRC4 errors and performs A-bit processing.

Key features

- E1 framer/deframer compliant to G.704, G.706, G.732 and O.163 ITU recommendations.

- Supports CAS and CCS signalling standards.

- Supports CRC4 based framing standards.

- User configurable receive and transmit control.

- Supports 8-bit parallel microprocessor interface for device configuration and control in host processor mode.

- Hardware control mode requires no host processor; ideal for stand-alone applications.

- Supports HDB3 line coding.

- Supports loop-back mode.

- Alarm generation, alarm detection and error logging.

- Compatible with Dallas DS2186 transmit line interface.

- Fully synchronous design.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

Block Diagram

What’s Included?

- Fully commented synthesizable VHDL or Verilog source code or FPGA netlist.

- VHDL or Verilog test benches and example configuration files.

- Comprehensive technical documentation.

- Technical support.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about TDM Framer IP core

SoCs Let Designers Re-Architect Next-Gen Transport Equipment

Fronthaul Evolution Toward 5G: Standards and Proof of Concepts

Frequently asked questions about TDM Framer IP cores

What is ITU G.704 E1 Framer/Deframer?

ITU G.704 E1 Framer/Deframer is a TDM Framer IP core from Noesis Technologies listed on Semi IP Hub.

How should engineers evaluate this TDM Framer?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this TDM Framer IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.