ISDB-T Modulator

The CMS0045 ISDB-T Modulator provides all the necessary processing steps to modulate one, two or three transport stream into a co…

Overview

The CMS0045 ISDB-T Modulator provides all the necessary processing steps to modulate one, two or three transport stream into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857/9957 or AD9789. Optionally the output can be selected as an IF to supply a single DAC.

The design has been optimised to provide excellent performance in low cost FPGA devices such as the Cyclone range from Altera or the Spartan range from Xilinx

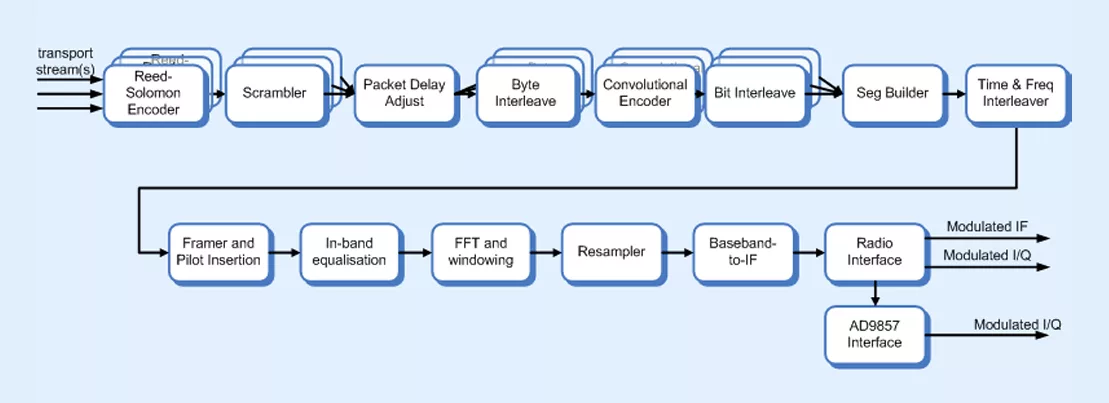

A description of the processing steps follows:

Reed-Solomon Encoder. This block generates Reed Solomon packets based on the industry standard MPEG RS(204, 188) code.

Scrambling. This block provides energy dispersal using the randomisation polynomial 1+x14+x15. Packet Delay Adjustment. Because the different Hierarchical Layers have different delays through the Byte Interleavers, each Layer is delayed to ensure the total delay through the system is an integer number of frames.

Byte Interleaver. This block performs the outer interleaving function with depth I=12 as specified by the ISDB-T standard.

Convolutional Encoder. This block performs convolutional encoding and data-rate puncturing. Bit Interleaver. This provides additional time dispersal of the signal for improved rejection of impulse noise.

Segment Builder. This block formats the hierarchical data for each layer into the specified number of active segments for that layer. Time Interleaver. This is a long-delay interleaver to spread the information over time to increase immunity to impulse noise.

Frequency Interleaver. The FITL disperses the data over multiple carriers to minimize signal degradation caused by nulls in the frequency response of the transmission environment.

QAM Mapper. This block performs the QAM constellation mapping for (D)QPSK, QAM16 or QAM64.

Framer and Pilot Insertion. The ISDB-T specification details a frame structure with scattered, continuous and TMCC pilots inserted at various carriers within each symbol. This block manages the pilot insertion dependent on the selected mode (2k, 4k or 8k), and symbol position within a frame.

IBEQ. An optional in-band equalizer circuit may be specified as a synthesis option. This allows the designer to easily compensate minor phase and gain slope associated with linear filter components on the board.

IFFT. This block performs the Inverse Fast Fourier Transform (IFFT) on the 2k, 4k or 8k carriers. A proprietary architecture is used which yields low Guassian noise, high MER outputs yet utilises low datapath widths. The IFFT also manages the on-air timing of the OFDM symbols by guard interval insertion. An optional windowing function is also included to reduce spurious emissions caused by the OFDM symbol transitions.

Resampler. This block resamples the 8.13 MHz complex IFFT output up to complex samples at the core clock frequency. This provides an ultra-flexible clocking strategy. This block also scales automatically as required to satisfy the selected channel bandwidth.

Baseband-to-IF. This block provides the option to mix the signal up to a higher IF as defined by a software register. This block may be removed using synthesis options if it is not required.

Radio Interface. This block performs some final, register-selectable processing functions to optimise the output for the radio in the target application. An optional processing step provides compensation for the sin(x)/x (or SINC) distortion that is introduced in the DAC. Additionally, the data can be formatted as either twos-complement or offset binary to suit various DAC devices. In may be formatted for external devices that could take separate I/Q, multiplexed I/Q or a single IF output.

Additional modes are added to support the Analog Devices AD9857/9957 that provides up-conversion, SINC filtering and DAC functions in a single package. The AD9857/9957 device requires that the I/Q data be multiplexed onto a single data bus. The ad9857_pdclk input is provided to enable this feature and should be sourced from the AD9857/9957 PDCLK output.

Interface modes are also available to support the Analog Devices AD9789 with RF up-conversion, SINC filtering and DAC functions in a single package.

Register Bank. The register bank provides a simple 32-bit interface for reading and writing registers within the modulator block. Full details of the registers within the modulator core are contained within the full data sheet.

External RAM. Most full-featured implementations will require an external RAM. This can be either SDRAM or synchronous SRAM, allowing implementation on a range of existing platforms.

The SDRAM interface is designed to work with standard interface blocks supplied by FPGA vendors. These interfaces are available to support most SDRAM technologies. The required SDRAM size is 4Mx8.

Alternatively, the CMS0045 also provides direct interfacing to 1MB or 2MB SRAM in 8 16 or 32-bit width.

Serial Programming. The core provides optional programming support for a range of Analog Devices parts, including AD9587/9957 and AD9789 DACs, AD9516 low-jitter clock generator and the ADF4350 low-phase-noise wideband synthesizer.

Key features

- Fully compliant with both ARIB STD-B31 and ABNT NBR 15601

- Enables rapid development of audio/visual systems using commodity Free-to-Air set-top-box technology and low-cost FPGAs.

- Supports SDRAM or Synchronous SRAM

- 1-segment or 13-segment operation

- 2K, 4K and 8K OFDM modes

- Hierarchical transmission - Fully configurable for up to three layers, each independently configurable to carry one of the TS inputs.

- Variable channel bandwidth support using a single clock reference.

- Optional DAC interfaces support AD9857/9957/9789 with auto-programming interface.

- Optional FFT output windowing.

- Optional in-band equalizer.

- Optional CPU-free configuration.

- Optional auxiliary channel support.

- Optional critical filter for “>25Watt” mask.

- Dual-core combining for multi-channel applications.

- Extension core available for SPI/ASI interface with integrated PCR TS re-stamping, NULL TS packet removal/filtering, NULL/PRBS TS packet insertion, input and output TS rate estimation registers. Seamless integration with Altera ASI megacore.

- Extension core for BTS support.

- Extension core for SFN synchronisation.

- Synthesis options for reduced functionality allow a range of compact, efficient designs, some without external RAM.

- Designed for very efficient FPGA implementation without compromising ASIC deployment.

- Supplied as a protected bitstream or netlist (Megacore for Altera FPGA targets).

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as: modulation, demodulation, equalisation and channel coding but our experience encompasses all of the major elements of a modern baseband 'core' including the medium access control (MAC), voiceband DSP, mixed-signal interfaces, and embedded Cpu and software.

Our services are provided on a turnkey basis or as part of a support package attached to our licenced IP or tool products.

Commsonic's customers are typically semiconductor vendors and manufacturers of communications equipment that require leading-edge, Standards-based or proprietary PHY solutions but lack the internal resources or skills necessary to deliver projects against aggressive deadlines.

Learn more about Modulation Demodulation IP core

Three Major Inflection Points for Sourcing Bluetooth Intellectual Property

Part 2: Opening the 5G Radio Interface

An Integrated, Tunable RF Filter: an Enabler for Reconfigurable Front-Ends

Design considerations for integrated CMOS receivers

Silicon IP for Programmable Baseband Processing

Frequently asked questions about Modulation and Demodulation IP cores

What is ISDB-T Modulator?

ISDB-T Modulator is a Modulation Demodulation IP core from Commsonic Ltd listed on Semi IP Hub.

How should engineers evaluate this Modulation Demodulation?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Modulation Demodulation IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.