Microprocessor IP for video codecs and video processing -- High Number of Streams Decoder For Data Center

The VC9800D enables up to 256 streams decoding with robustness, high throughput single-core solution, or multi-core solution, sup…

Overview

The VC9800D enables up to 256 streams decoding with robustness, high throughput single-core solution, or multi-core solution, supporting VVC, AV1, HEVC, H.264, AVS3, AVS2, VP9 video formats, JPEG, and legacy formats.

VeriSilicon's Hantro is based on silicon-proven VeriSilicon Hantro technology and target to demand the high number steams, high throughput, low bandwidth data centers to address the video transcoding, AI server, desktop virtualization even cloud gaming applications.

The VC9800D provides semiconductor manufacturers a minimum risk solution for integrating high-performance video capability into their chips.

Key features

- Video Formats

- Unified architecture supports multiple formats

- VVC Main Profile 8/10bit

- AV1 main profile

- HEVC main10, main, and main still profiles

- H.264 up to constraint high10 profile

- VP9 profile 0 and profile 2 (10-bit)

- AVS3.0 main-10 bit profile

- AVS2.0 main/main10 profile

- JPEG (Include Progressive JPEG)

- Legacy formats: MPEG4, MPEG2, MPEG1, VC-1, H.263, VP8, VP7, VP6, RV10, RV9, RV8, AVS, AVS+, Sorenson, DIVX3/4/5/6, WebP

- High Performance and Throughput

- Up to 8K@30fps/16x1080P@30fps performance with a single-core

- Up to 8K@120fps/64x1080P@30fps with multiple cores

- High BUS latency tolerance without mainstream decoding format performance impact

- Up to 256 streams in a single device

- Maximally offloads the system CPU

- Leading in PPA/Die Area for high performance solution

- Versatile Inline Post Processing

- Bandwidth efficient solution by inline processing

- Multiple post processing outputs

- High quality resize and programmable scaling kernel

- RGB formats for AI models

- Compatible VSI GPU rendering formats for high working efficiency with VSI GPU

- Rich post-processing capability, such as blending, image stitch, color remapping, rotation, flip, etc

- Features for Different Application Requirements

- Based on frame level switching of virtual machine tasks, providing ultra-low latency task scheduling capabilities for cloud computing applications

- Error concealment and robustness

- Independent multiple Post-processing channel for Video transcoding

- Support compatible AI input NCHW(Planar)/NHWC(Packed) output to best fit AI applications

- Matching OpenCV resize precision for AI applications

- Normalization for AI pre-processing

- DDR efficiency and bandwidth saving

- Low-latency decoding

- Security and DRM support

- Flexible HW Configuration

- HW configuration can be done for most video formats

- Typical 1-4 cores or more in a device

- PP different channels can have different features and restriction

- Data caching and burst shaping for good DDR efficiency in specific system

- Bandwidth saving by reference frame & output frame compression

- Optional MMU, encryption

- API support

- OpenMax-IL

- FFmpeg avcodec Plug-in

- VAAPI

- Hantro Video Private ctrlSW API

- V4L2 API

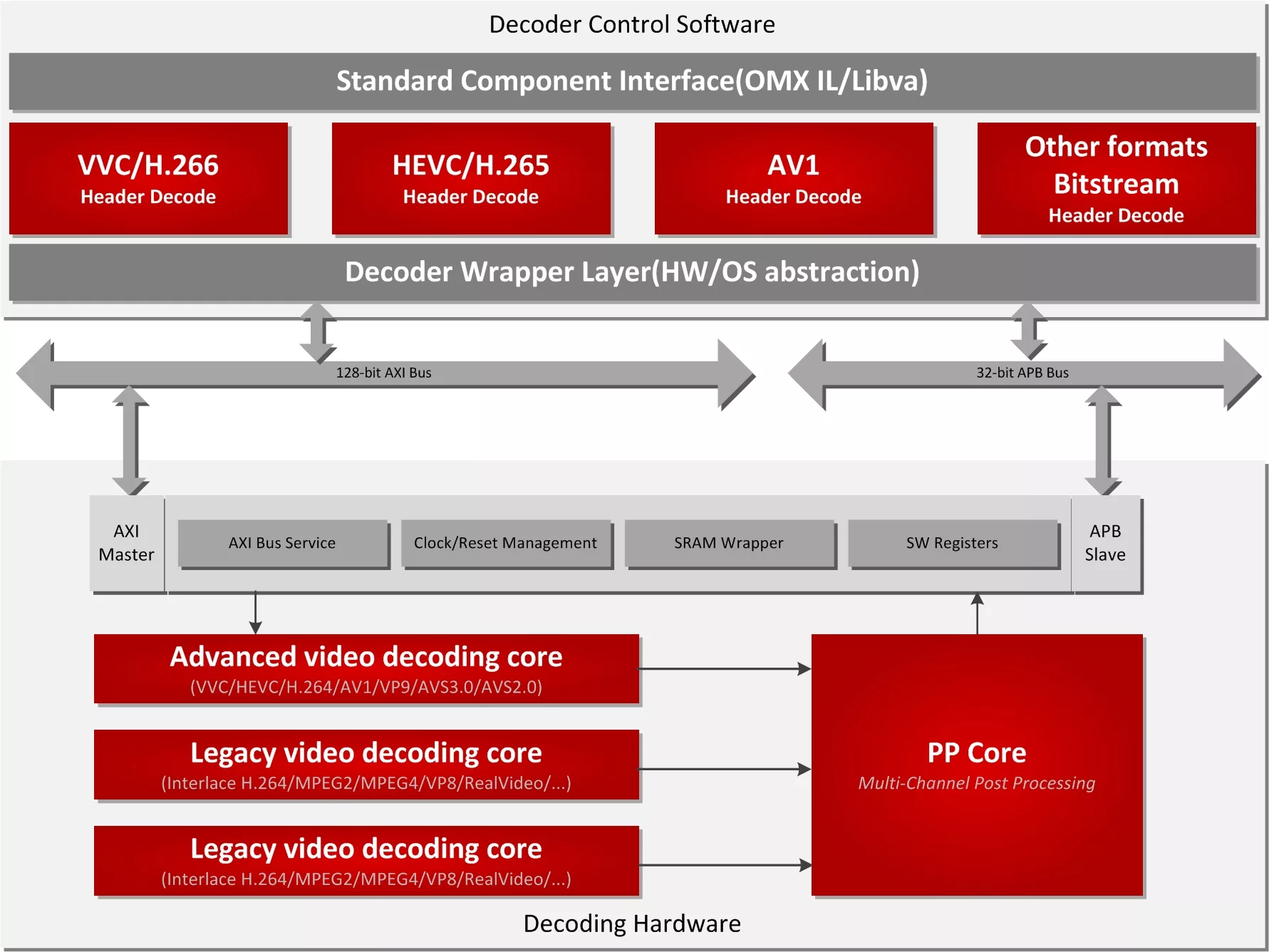

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Microprocessor IP for video codecs and video processing -- High Number of Streams Decoder For Data Center?

Microprocessor IP for video codecs and video processing -- High Number of Streams Decoder For Data Center is a Video Processing IP core from VeriSilicon Microelectronics (Shanghai) Co., Ltd. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.