Half-band Nyquist Decimation Filter

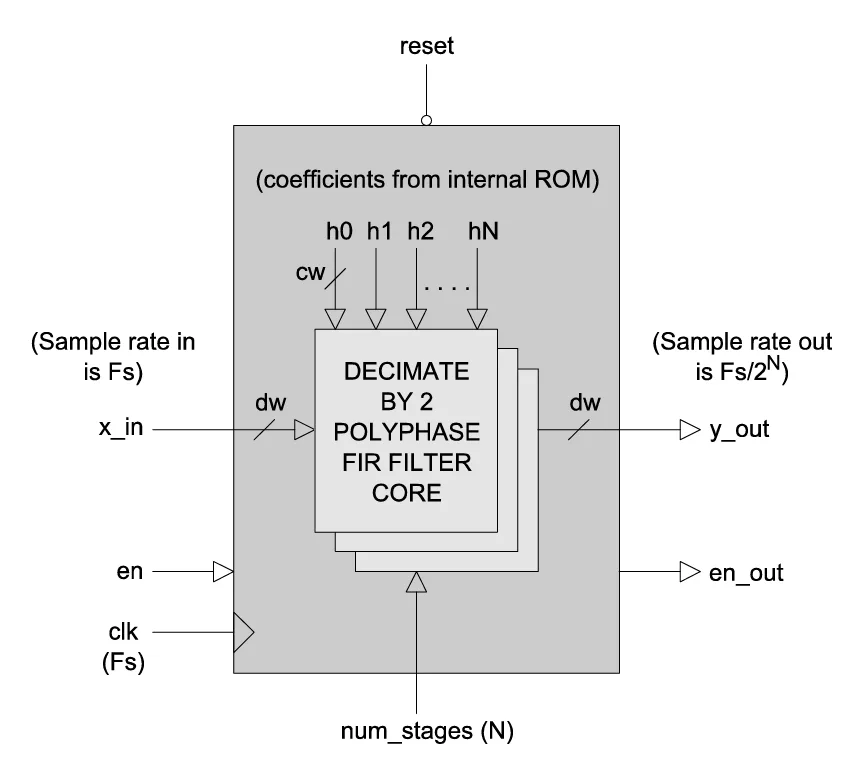

FIR_DEC_N is a polyphase decimation filter that permits the down sampling of an input signal by any power of 2.

Overview

FIR_DEC_N is a polyphase decimation filter that permits the down sampling of an input signal by any power of 2. The filter core is organized as a highly optimized systolic array, allowing the user to specify very large decimation factors while keeping resource costs to a minimum.

Input data is sampled on the rising clock-edge of clk when en is active high. Internally, the samples are filtered and decimated then presented at the output interface, y_out.

The output signal en_out is the output clock-enable signal that indicates when an output sample is valid. For instance, when decimating by a factor of 2, then en_out will have a duty cycle of 50% relative to the input clock-enable signal. When decimating by a factor of 4, the duty cycle will be 25% and so on.

Key features

- Synthesizable, technology independent VHDL Core

- Half-band polyphase decimation filter with a configurable decimation factor from 2 to 2N

- FIR filter core implemented as an optimized 48-tap systolic array (24-taps per phase) for ultimate speed and minimal resource use

- Configurable data and coefficient widths

- Symmetric arithmetic rounding limits DC-bias problems

- Saturation of output samples - no wrap

- Ships with 14-bit coefficients giving 80 dB stop-band attenuation

- Only 12 H/W multipliers used per decimate-by-2 stage

- Supports input sample rates of up to 300 MHz+

Block Diagram

Applications

- Decimation of signals after digital-down-conversion

- Decimation by a wide range of factors from 2 to 2N

- Reduction of input sample rate to make subsequent signal processing easier

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is Half-band Nyquist Decimation Filter?

Half-band Nyquist Decimation Filter is a Filters Transforms IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.