Overview

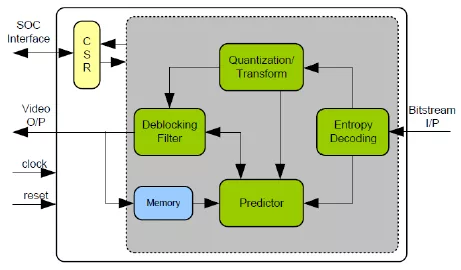

The H.264 Decoder IP Core is a full-featured, easy-to-use, synthesizable design that is easily integrated into any SoC or FPGA development. The H.264 Decoder IP can be implemented in any technology. The H.264 Decoder core supports the ISO/IEC 14496-10/ITU-T H.264 specification. It can also supports a variety of host bus interfaces for easy adoption into any design architecture - AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone or custom buses. The H.264 Decoder IP is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. The H.264 Decoder IP is validated in using FPGA. The core includes RTL code, test scripts and a test environment for complete simulation.

Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about Video Processing IP core

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

Configurable Processors for Video Processing SOCs

Programmable FPGA devices are the perfect choice for interfacing with multiple high-resolution image sensors simultaneously...

A look at the design of multiprocessor systems-on-chips (MPSoCs) for video applications and how to optimize them for computational power and real-time performance as well as flexibility. Part 1: Architectural approaches to video processing

Building a high-performance, quad-channel H.264 encoder using low-cost, low-power FPGA architecture.

Adding to its growing portfolio of licensable silicon IP subsystems, ARC has announced five configurable video processing subsystems. The subsystems range from the smallest-size AV 402V to the highest-performance AV 417V, and support multi-standard video encoding and decoding at resolutions ranging from CIF to D1.