2.5 Gbps GPON FEC Codec

This high performance core is a full featured Forward Error Correction encoder and decoder, specially designed for high speed opt…

Overview

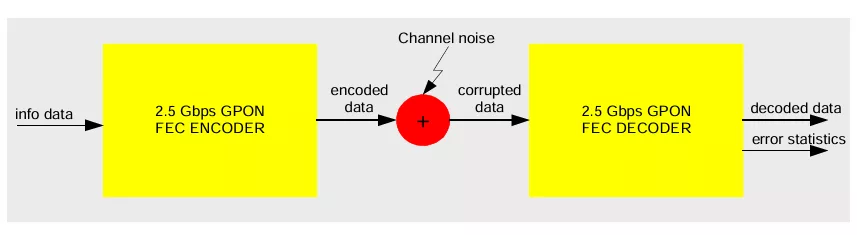

This high performance core is a full featured Forward Error Correction encoder and decoder, specially designed for high speed optical networks or any other broadband applications. It is fully compliant with the 2.5 Gbps GPON standard (G.984.3) and is available for FPGA or ASIC implementation. The FEC algorithm is based on Reed-Solomon (255,239) code and consists of an encoder and decoder module. The encoder module computes 16 parity bytes and appends them on the 239 byte information block. The decoder receives the 255 bytes codeword, locates and corrects up to 8 byte errors being introduced in the transmission channel.

Key features

- Fully compliant with the ITU-T G.984 (GPON), ITU-T G.983 (BPON) and ITU-T G.709 recommendations.

- Supports ASIC and FPGA implementation technologies.

- Single edge, fully synchronous design.

- Area efficient design.

- Symbol rate clock.

- Supports both streaming of data and gaps between codeword bytes.

- Calculates the number of erroneous bytes.

- Generates a status signal indicating error locations.

- Determines the location and magnitude of the erroneous bytes.

- Corrects up to 8 erroneous bytes.

- Detects uncorrectable codewords.

- Predictable low decoder latency.

Block Diagram

Benefits

- Flexible

- Compact

- Cost-effective

What’s Included?

- Verilog Source Code

- Test Bench

- Sample Syntheis scripts

- Dcumentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is 2.5 Gbps GPON FEC Codec?

2.5 Gbps GPON FEC Codec is a Channel Coding IP core from ASICS World Services, LTD. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.