From driveway to checkout: seamless indoor navigation powered by UWB

Discover how UWB and standardized indoor positioning enable seamless navigation from outdoor GNSS to precise indoor guidance across campuses, malls, hospitals, and more.

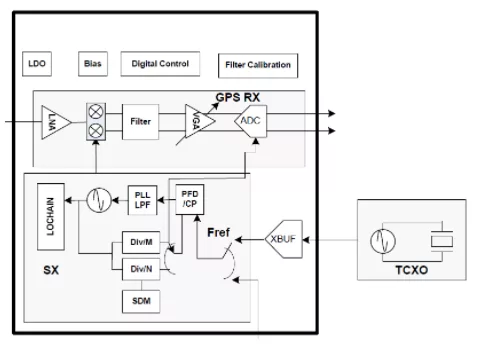

This GNSS RF Receiver IP is silicon-proven in TSMC40nm ULP process node, offers comprehensive support for all current satellite-b…

Note: some files may require an NDA depending on provider policy.

GNSS (GPS, Galileo, GLONASS, Beidou3, QZSS, SBAS) Ultra-low power RF Receiver IP is a GNSS IP core from T2M GmbH listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GNSS IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.