X-band (7.9 − 9.8GHz) High Performance Frac-N PLL

The NEXUS9X is a CMOS high performance PhaseLocked Loop (PLL) with integrated voltage controlled oscillator (VCO) and loop filter…

Overview

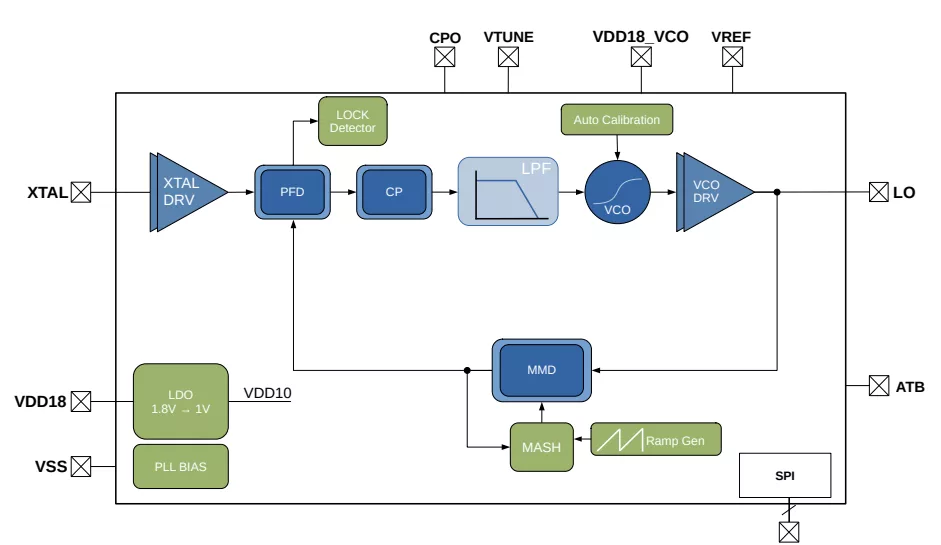

The NEXUS9X is a CMOS high performance PhaseLocked Loop (PLL) with integrated voltage controlled oscillator (VCO) and loop filter, designed to provide high flexibility in its use in order to adapt to a variety of applications. It covers typically the frequency range [7.9 − 9.8]GHz over variations in process, voltage and temperature (PVT), which can be scaled up/- down by using frequency multipliers/dividers, depending on the application. It requires a [40 − 320]MHz external reference and utilizes a fractional-N divider providing high frequency resolution and minimum phase noise (PN). Additional features, such as automatic VCO calibration, lock detection and frequency ramp generator for frequency-modulated continuous-wave (FMCW) Radar applications makes this PLL highly functional and adaptable. Also, external filter and/or VCO can be used, if required. Communication with the PLL is done through Serial Peripheral Interface (SPI).

Key features

- Fractional-N PLL

- Excellent phase noise (PN) performance

- Output frequency range: 7.9 − 9.8 GHz

- Input reference frequency range: 40 − 320 MHz

- Wide range of CP current levels

- Integrated loop filter

- Automatic VCO calibration

- Automatic VCO temperature drift compensation

- Phase lock detection

- Internal frequency ramp generator for FMCW RADAR

- Supports use of external filter and/or VCO

Block Diagram

Applications

- 5G PtP and PtMP communication systems

- Wireless devices (WiFi, LTE, IoT)

- Fixed wireless access

- SATCOM

- Radar (FMCW support)

What’s Included?

- Evaluation board

- Netlist

- Layout Exchange Format, .lib files

- GDSII

- Footprint (LEF)

- Testbenches (optional)

- Documentation

- Behavioural model (verilog/verilogA)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is X-band (7.9 − 9.8GHz) High Performance Frac-N PLL?

X-band (7.9 − 9.8GHz) High Performance Frac-N PLL is a PLL IP core from Akronic, P.C. listed on Semi IP Hub.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.