DO-254 compliant MIL-STD-1553B IP core

MIL-STD-1553B IP Core implements MIL-STD-1553B standard and provides single or multi-functional interface between host processor …

Overview

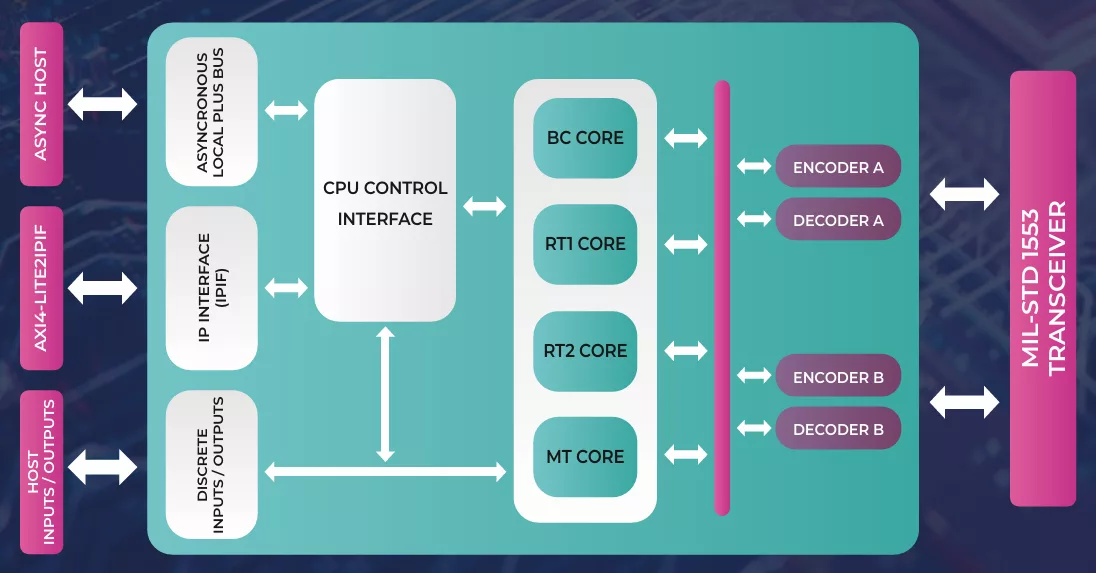

MIL-STD-1553B IP Core implements MIL-STD-1553B standard and provides single or multi-functional interface between host processor and MIL-STD-1553 bus transceiver. DO-254 compliant MIL-STD-1553B IP core can function as Bus Controller (BC), two separate Remote Terminals (RT) and Bus Monitor (BM), simultaneously.

The MIL-STD-1553B IP Core uses standard AXI4 – Lite interfaces to ease integration or Asynchronous Host Interface (Local Plus Bus). Its configuration and status registers are accessible via a 16-bit-wide IPIF (IP Interface) bus. Auto Enable configuration is supported via EEPROM.

The MIL-STD-1553B IP Core is available in synthesizable RTL (VHDL) source code or as a targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

Key features

COMMON SPECS

- 64K bytes internal static RAM with RAM Error Detection/Correction option

- 16-bit time tag counters and clock sources for all terminals

- 64-Word Interrupt Log Buffer

- Built-in and optional self-test for protocol logic, digital signal paths and internal RAM

- Programmable 50/100 MHz Clock Frequency

- DO-254 Compliant certification package

BUS CONTROLLER SPECS

- Fully programmable Bus Controller

- Bus Controller has 32-bit time count options

- Programmable Status Set

- Message Format Check

- 16 Condition Code for all opcode

- 64-Word General Purpose Queue for external BC Host

- Programmable Inter-Message Gap Time (resolution 1us)

- Programmable Message Timeout

REMOTE TERMINAL SPECS

- Two independent Terminal Core

- Programmable different buffer mode for all Subaddress

- Subaddress based illegal command declaration

- Optional temporary buffer

BUS MONITOR SPECS

- Basic Bus Monitor (BBM) records commands and data separately, with 16-bit or 48-bit time tagging

- Optional support function for IRIG-106 data packets, including full packet headers and trailers

- Bus Monitor has 32-bit and 48-bit time count options Message Filter Table

Block Diagram

What’s Included?

- Encrypted Netlist

- Synthesis Scripts

- Comprehensive Documentation

- Device Driver for Xilinx SDK (Bare-metal)

- Optional SystemVerilog/UVM Advanced Verification Environment delivery. Needs extra MIL-STD-1553B VIP license.

- Optional DO-254 Certification Data Package is available

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- Design IP Cores

- Design & Verification Services: ASIC / FPGA and Embedded Systems’ development

- Functional Safety Consultancy & Training Services

- Trainings: Wide range of trainings with more than 150 different trainings

Learn more about Mil Std 1553 IP core

Frequently asked questions about MIL-STD-1553 IP cores

What is DO-254 compliant MIL-STD-1553B IP core?

DO-254 compliant MIL-STD-1553B IP core is a Mil Std 1553 IP core from ElectraIC listed on Semi IP Hub.

How should engineers evaluate this Mil Std 1553?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mil Std 1553 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.