Root of Trust - Foundational security in SoCs and FPGAs for Chinese IoT clients and sensors

Designed to be integrated in power and space-constrained SoCs or FPGAs, the RT-121 Root of Trust (formerly VaultIP) is a FIPS 140…

Overview

Designed to be integrated in power and space-constrained SoCs or FPGAs, the RT-121 Root of Trust (formerly VaultIP) is a FIPS 140-3 compliant hardware core that guards the most sensitive assets on chips and establishes the foundation for platform security.

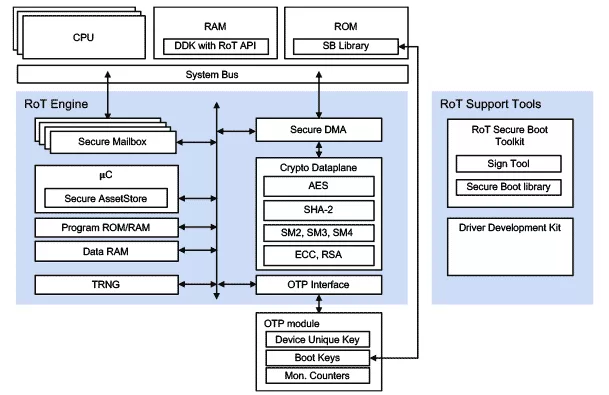

Featuring a firmware-controlled architecture with dedicated secure memories, the RT-121 hardware Root of Trust provides a variety of cryptographic accelerators including AES, SHA-2, RSA and ECC, and the OSCCA SM2/3/4 Chinese cryptographic accelerators. Ideal for power and space-sensitive applications like IoT clients, edge nodes and sensors, the RT-121 Root of Trust offers the best balance of size and performance available on the market.

The RT-121 offers a series of key security use cases ‘out of the box’, including:

- Secure Boot assist to host CPU(s) and protection of key material

- Secure firmware upgrade management for Host CPU

- Lifecycle management support

- Secure Debug support

- Secure device authentication and identity protection

The RT-121 provides a secure asset store:

- Only the RT-121 can manage, use and access the assets

- The O/S and applications cannot access to key values

- Applications request asset use by reference

- Enforces policies for access and use of keys and cryptographic functions

- Key generation, derivation, storage and transport

How the Root of Trust Works

The RT-121 Root of Trust is a silicon IP core developed to protect an SoC platform and its operation. It allows the SoC to boot securely and protects sensitive key material and assets. At its heart, its Secure Asset Store allows import, negotiation, and creation of secret and private key material. Safe use of key material is enforced through a flexible key use and access policy. Keys can be securely stored in off-chip NVM. Fully featured, its cryptographic data plane associated to its DMA offloads the main CPU while never exposing secret data to the OS or the applications. It is designed to provide secure, energy efficient and accelerated security functions.

Readily deployable, the RT-121 Root of Trust is offered in off-the-shelf configurations, allowing a choice tailored to the needs of your application. Configurations differ by cryptographic accelerators contained and 3rd-party certification and standard compliance.

The RT-121 is part of the broad Rambus Root of Trust portfolio, which ranges from small, lightweight cores designed to protect IoT endpoints all the way to fully programmable Root of Trust cores designed to protect the most sensitive government/defense chips and automotive deployments requiring ISO-26262 certifications.

Rambus can optionally offer dedicated FIPS 140-3 support packages to its licensees that provide FIPS 140-3 related certification documentation, FIPS test scripts, and dedicated FIPS support.

| Feature | Description | Details |

| FIPS 140-3 | CAVP and CMVP Compliant | Includes CAVP certificates for NIST approved algorithms and TRNG |

| Cipher Algorithm support |

AES (all key sizes) SM4 (128-bit key) |

Modes: CBC, CTR, CCM, CMAC Modes: CBC, CTR |

| Hash Algorithms | SHA-1, SHA-2 SM3 |

SHA-2 224-256 |

| Message Authentication Code Algorithms | HMAC-SHA-1, HMAC-SHA-2 HMAC-SM3 |

SHA-2 224-256 |

| AEAD Algorithms | AES-CCM | Modes: CCM |

| Signature Generation and Verification | ECDSA, SM2DSA RSA up to 3096 bits |

NIST P-224, P-256, P-384, P-521 |

| Key Agreement Algorithms | ECDH DH |

NIST P-224, P-256, P-384, P-521 Up to 3096 bits |

| Key Transport Algorithms | ECIES RSA Wrap/Unwrap (RSA-OAEP) SM2-WRAP AES-WRAP SM4-WRAP |

128- and 256-bit strength variants Up to 3096 bits 128- and 256-bit strength variants 128-bit strength |

| True Random Number Generator | NIST SP800-90A/B/C | NIST ENT certificate |

| Crypto Performance | Cipher/Hash Performance (Gbps) @500MHz | Scalable, ~2 Gbps |

| I/O Bus | AMBA Bus Master/Slave | AXI/AHB Master, AXI/AHB/APB Slave |

| OTP Interface | Interface to 3rd-Party OTP |

TCM |

Block Diagram

Benefits

- Side channel attack resistant

- Technology and node independent

- Superior cryptographic protection

- Use with any ASIC or FPGA

Applications

- IoT, IIoT, sensors, gateways

What’s Included?

- Complete Documentation

- Tools and Scripts: Verilog for synthesis and simulation

- Complete verification test bench and comprehensive set of test vectors

- Container-authoring software

- Boot loader and firmware, including secure RTOS and security monitor

- HLOS APIs for accessing capabilities

- Complete development environment, including compiler, assembler, debugger, simulator, reference code

- QEMU implementation (source code)

- Implementation of HLOS or ASIC components (source code)

- Sample application demonstrating usage of Secure Application

- HLOS Programmer’s Guide

- Developer’s Guide

- API Guide

- Integration Guide

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Root Of Trust IP core

Rambus CryptoManager Root of Trust Solutions Tailor Security Capabilities to Specific Customer Needs with New Three-Tier Architecture

Why Anti-tamper Sensors Matter: Agile Analog and Rambus Deliver Comprehensive Security Solution

Side-Channel Attacks On Post-Quantum Cryptography

Cryptography Does Not Equal Security

Root of Trust: A Security Essential for Cyber Defense

Frequently asked questions about Root of Trust IP cores

What is Root of Trust - Foundational security in SoCs and FPGAs for Chinese IoT clients and sensors?

Root of Trust - Foundational security in SoCs and FPGAs for Chinese IoT clients and sensors is a Root Of Trust IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Root Of Trust?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Root Of Trust IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.