HCL Technologies

HQ:

India

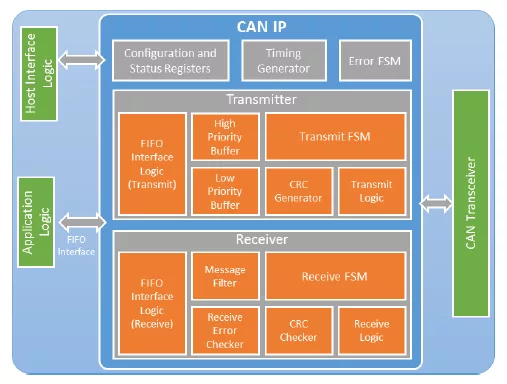

HCLTech is one of Indias leading global Technology and IT enterprises, operating across 61 countries and with annual revenues of US$13 billion. Our range of offerings span R&D and Technology Services, Enterprise and Applications Consulting, Remote Infrastructure Management, BPO services, IT Hardware, Systems Integration and Distribution of Technology and Telecom products in India. HCLTech specializes in spec to parts custom SoC design service. HCLTech design house is focused on designing high-performance hardware engineering solutions. Our robust processes, development methodology, expertise in complete system engineering including ASIC / FPGA (mixed signal), ESL (Electronic System Level), Board Design & Firmware have enabled our customers to improve the design cycle and achieve faster go to market. We have also provided significant value to our customers through our reusable IP cores, automated test / verification frameworks and other solution accelerators. Our expertise spans across tools from Cadence, Mentor, Synopsys and others.