Centralised Network Configurator

Software solution targeting the configuration of Ethernet switches and endpoints in TSN networks Centralized Network Configurator…

Overview

Software solution targeting the configuration of Ethernet switches and endpoints in TSN networks

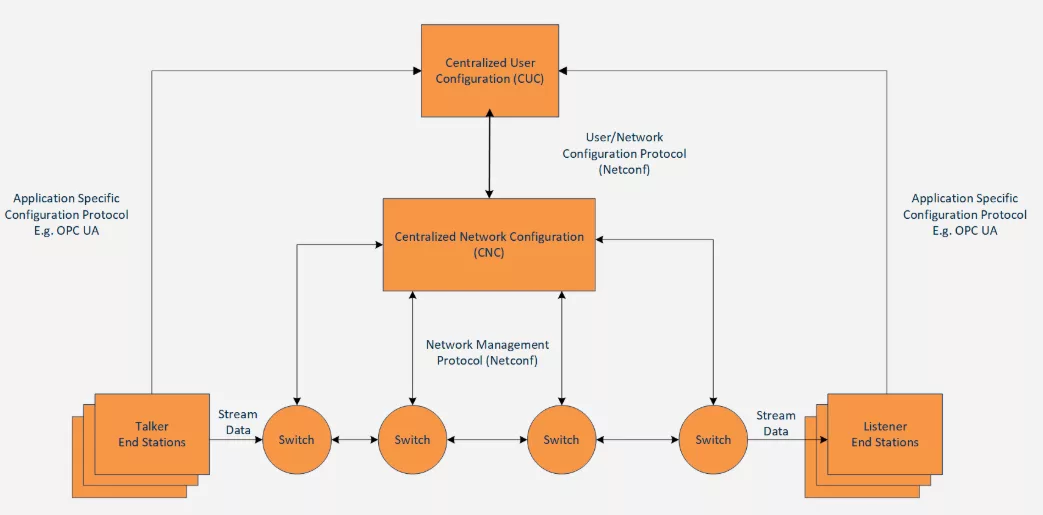

Centralized Network Configurator or CNC is a component used in Time Sensitive Networking (TSN) networks. The CNC monitors data streams while coordinating and managing network configuration. The CNC is based on the stream reservation protocol (802.1 Qcc) to optimize the efficient use of network resources and provide Quality of Service (QoS).

The software component of the CNC can give solutions for complex tasks such as Topology selection, Traffic type assignment, Routing, Scheduling and Bandwidth allocation.

The Comcores CNC targets TSN nodes such as endpoints and switches. It receives stream requests, collects the capabilities of the network entities, calculates the optimal configuration, and applies the configuration to the network entities.

Comcores CNC is demonstrated on a Raspberry Pi model B revision 1.2 and the machine hosting CNC must support a Linux operating system. Comcores CNC is a software solution suitable targeting the configuration of Ethernet switches and endpoints in TSN networks.

Key features

Delivers Performance

- Support for both dynamic and incremental client-based stream planning

- CNC Planning features based on different user-defined constraints, such as:

- End-to-end latency

- Incremental planning mode enables the addition of new data streams without affecting existing scheduled data streams

- Netconf/YANG model-based deployment

- Standardized Netconf 1.1 client interface towards TSN devices, and Netconf 1.1 server interface towards CUC

Feature Rich

- Target device types: TSN switches, endpoints or switched endpoints that support the following derived YANG models:

- Frame Premption – IEEE 802.1Qbu

- Credit Based Shaper – IEEE 802.1Qav

- Time Aware Scheduler – IEEE 802.1Qbv

- Traffic Filtering and Policing – IEEE 802.1Qcicheduled Traffic – IEEE 802.1Qcw

- Time Synchronization – IEEE 802.1ASdn

- Bridges and Bridged Networks – IEEE 802.1Qcp

- VLAN and MAC services

- UNI compliant stream requests – IEEE 802.1Qdj

- Provisioning request (eg. Centralized User Configurator – CUC)

- Link Layer Discovery Protocol – IEEE 802.1ABcu

- Network discovery based on a standardized topology file input

Block Diagram

What’s Included?

-

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about System Controller IP core

Low Power Asynchronous Processor With Cordic Co-Processor

Automation in IP based SoC development: Case study of a media processor subsystem

DDR2 Signal Integrity

Extreme partitioning

Reconfiguring Design -> Reconfiguring for broadband access

Frequently asked questions about system controller IP cores

What is Centralised Network Configurator?

Centralised Network Configurator is a System Controller IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this System Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this System Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.