CCSDS SCCC Turbo Encoder and Decoder

The recommended CCSDS 131.2-B-1 standard introduces a Serial Concatenated Convolutional Code (SCCC).

Overview

The recommended CCSDS 131.2-B-1 standard introduces a Serial Concatenated Convolutional Code (SCCC). Main goal of this code is to allow an efficient use of available bandwidth, by allowing to select from 27 valid configurations with a wide range of constellations, block lengths and code rates.

The outstanding error correction performance of the SCCC code in combination with the high data rates makes this IP core the ideal fit for further applications where high throughput and high spectral efficiency is key for operation.

Key features

- Compliant with CCSDS 131.2-B-1

- Support for all 27 ACM formats

- Support for all modulation schemes (QPSK, 8-PSK, 16-APSK, 32-APSK, 64-APSK)

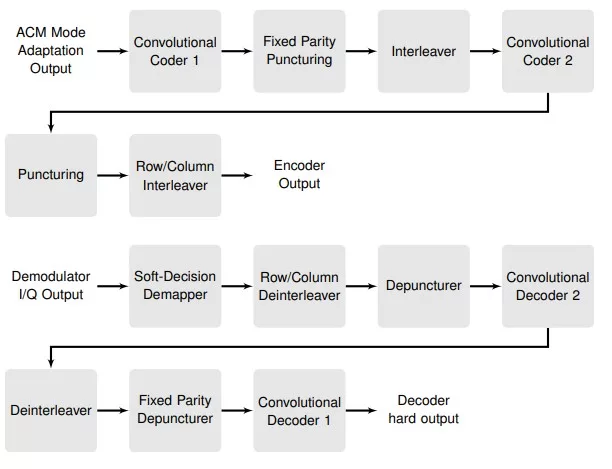

Block Diagram

Benefits

- Burst-to-burst on-the-fly configuration

- High payload block length granularity (between 5,758 and 43,678 bits)

- High code rate granularity (code rates between 0.36 and 0.90)

- Configurable amount of turbo decoding iterations for trading off throughput and error correction performance

- Low-power and low-complexity design

- Available for ASIC and FPGAs (AMD Xilinx, Intel, Microchip)

- Deliverable includes VHDL source code or synthesized netlist, VHDL testbench, and bit-accurate Matlab, C or C++ simulation model

Applications

- Satellite communication

- High data rate telemetry applications

- Earth Exploration Satellite Service (EESS)

- Applications with the highest demands on forward error correction

- Applications with the need for a wide range of code rates and block lengths

What’s Included?

- Block-to-block on-the-fly configuration.

- High payload block length granularity (between 5,758 and 43,678 bits).

- High code rate granularity (code rates between 0.36 and 0.90).

- Configurable amount of turbo decoding iterations for trading-off throughput and error correction performance.

- Low-power and low-complexity design.

- Available for ASIC and FPGAs (Xilinx, Intel, Microchip).

- Deliverable includes VHDL source code or synthesized netlist, VHDL testbench, and bit-accurate Matlab, C or C++ simulation model.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is CCSDS SCCC Turbo Encoder and Decoder?

CCSDS SCCC Turbo Encoder and Decoder is a Channel Coding IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.