AXI to AHB Lite Bus Bridge

The AHB Lite to AXI Bridge translates an AHB Lite bus transaction (read or write) to an AXI bus transaction.

Overview

The AHB Lite to AXI Bridge translates an AHB Lite bus transaction (read or write) to an AXI bus transaction. It is expected that the AXI clock and the AHB clock are derived from the same clock source, and that the period of the AHB Lite clock is an integer multiple of the AXI clock in the range [1,16].

Logic on two synchronous clock domains is used to accomplish the translation.

The AHB Lite logic is responsible for responding to transaction requests from the AHB Lite, and for generating AXI transactions based on transaction information from the AHB logic, and for presenting read data from the AXI subsystem back to the AHB Lite Master.

The AXI logic is responsible for generating AXI transactions based on transaction information from the AHB Lite logic, and for pacing the AXI transaction based on internal FIFO levels and on responses from the AXI Slave peripheral.

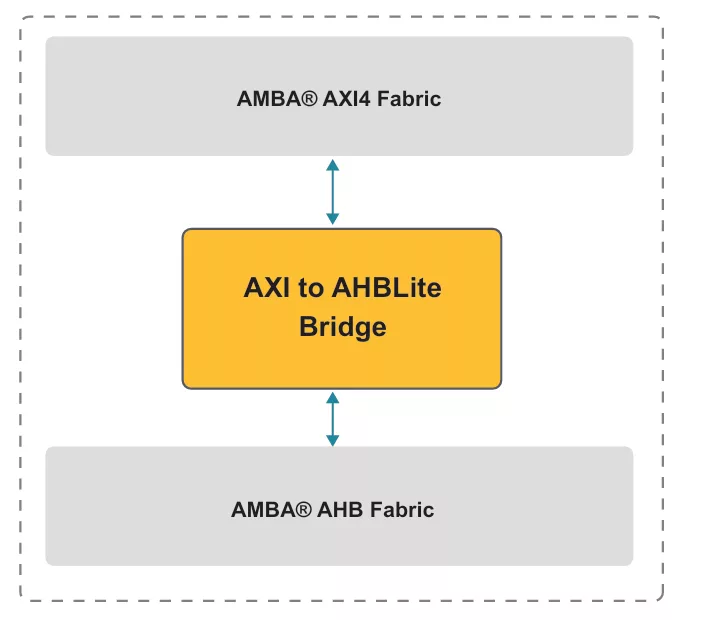

The AHB Lite to AXI Bridge acts as an AHB Lite Slave, and an AXI Master in an AXI/AHB subsystem. Typically, the AHB Lite to AXI Bridge has its AHB Lite interface connected to a Slave port on an AHB Lite Channel/Interconnect module, and its AXI interface connected to the Master port on an AXI Channel module.

Key features

- Converts AXI Master component transactions to AHB Lite Controller transactions

- Pseudo-synchronous clock domains

- FIFOs for Buffering

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- AXI Bus Functional Model

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is AXI to AHB Lite Bus Bridge?

AXI to AHB Lite Bus Bridge is a Protocol Bridge IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.