APB Timer

The APB Timer module is a sixteen-bit down counter with a selectable prescaler.

Overview

The APB Timer module is a sixteen-bit down counter with a selectable prescaler. Prescale values of 1, 16 and 256 can be selected. The prescaler extends the timer’s range at the expense of precision.

The Timer provides two modes of operation that provide a free running value and also periodic interrupts.

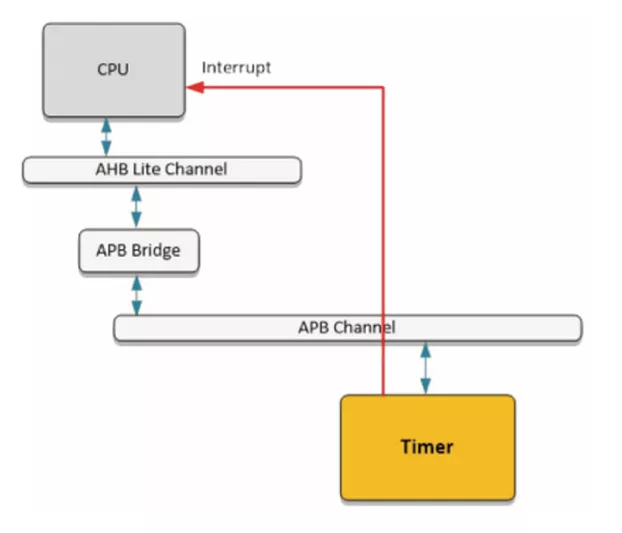

The Timer contains several configuration registers that can be written and read by the processor. Two 4-bit prescalers precede a 32-bit counter. The counter can be clocked at either the input clock rate, or a choice of 7 prescaled rates. The counter can be loaded with a value from a preload register. The counter can optionally generate an interrupt.

The Timer module is a standard APB Slave peripheral; the Timer registers are accessed through this interface.

Key features

- AMBA® APB Compatible

- 32 bit counter/timer

- 10 bit selectable pre-scale

- Periodic and free running event timer modes

- Useful for software or RTOS time base

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- APB Bus Functional Model

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Timers & Watchdogs IP core

Multitasking operations require more hardware based RTOSes

How to Ensure a Bug Free BootROM?

SystemC: Key modeling concepts besides TLM to boost your simulation performance

Frequently asked questions about Timers & Watchdogs IP cores

What is APB Timer?

APB Timer is a Timers & Watchdogs IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Timers & Watchdogs?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Timers & Watchdogs IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.