8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level f…

Overview

The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications. Approved based on the functional safety assignments of a Safety Element Out-of-Context (SEooC), which includes the ISO 26262 compliant development process and the qualitative approach with respect to hardware safety analysis, D45-SE is certified to be used in safety-related applications such as Millimeter Wave Radar Sensor, Around View Monitor system (AVMS), Vehicle Instrument Cluster, Powertrain DCU, Infotainment DCU, Front/Rear different applications for ZCU.

The D45-SE includes “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, and “B” bit manipulation. D45-SE equipped with comprehensive SIMD/DSP instructions that can boost the performance of voice, audio, image and signal processing. Its ”B” extensions provide some combination of code size reduction, performance improvement, and energy reduction, and “FD” extensions support IEEE754-compliance single and double precision floating point instructions. D45-SE incorporates MemBoost to greatly enhance memory bandwidth and reduce memory latencies for applications with intensive memory accesses. Other features include ECC for memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™ and StackSafe™ for software quality improvement, PowerBrake and WFI for power management.

Key features

- 32-bit in-order dual-issue 8-stage pipeline CPU architecture

- AndeStar™ V5 Instruction Set Architecture (ISA)

- Compliant to RISC-V RV32 GCBP little endian:

- RV-GC: Integer, single/double precision floating point and 16-bit extensions

- RV-B Bit manipulation extensions

- RV-P (draft) DSP/SIMD extensions

- Andes V5 performance/code size extensions

- 16/32-bit mixable instruction format for compacting code density

- Advanced low power branch predication to speed up control code

- Return Address Stack (RAS) to accelerate procedure returns

- Physical Memory Protection(PMP), and programmable Physical Memory Attribute (PMA)

- MemBoost for heavy memory transactions

- Flexibly configurable Platform-Level Interrupt Controller (PLIC) for supporting wide range of system event scenarios

- Enhancement of vectored interrupt handling for real-time performance

- Advanced CoDense™ technology to reduce program code size

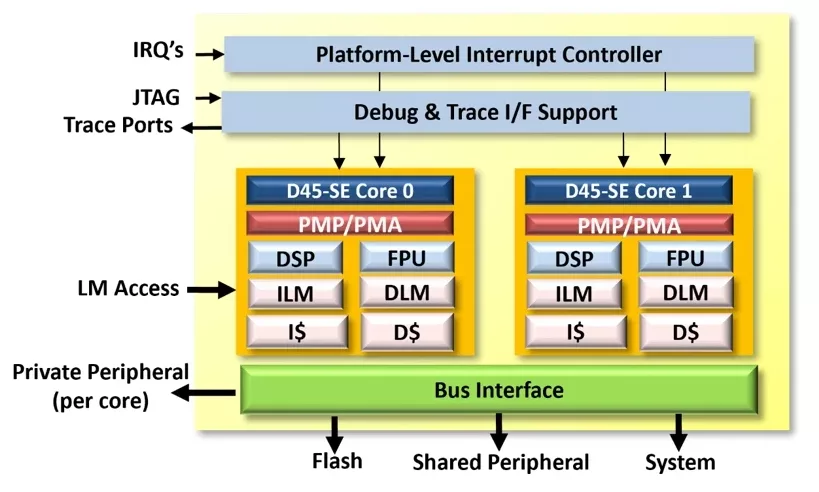

Block Diagram

Applications

- Supports a wide range of applications from ASIL B to ASIL D, including Millimeter Wave Radar Sensor, Around View Monitor system (AVMS), Vehicle Instrument Cluster, Powertrain DCU, Infotainment DCU, Front/Rear different applications for ZCU.

- Compliant with ISO 26262:2018 standard parts 2, 4, 5, 7, 8 and 9 for ASIL-D

- Independent assessment and certification by SGS-TÜV Saar GmbH

- AndesCore™ D45-SE ISO 26262 compliant certificate (need to add diagram connection)

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Safety MCU IP core

Advanced BLDC Motor Control using Freescale Ultra Reliable MPC5676R/MPC5674F MCU

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Keep Legacy Systems Running with a DO-254 HDLC & SDLC Part Replacement IP Core

Rambus CryptoManager Root of Trust Solutions Tailor Security Capabilities to Specific Customer Needs with New Three-Tier Architecture

Moving the World with MIPS M8500 Real-Time Compute Solutions

Frequently asked questions about Safety MCU IP cores

What is 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications?

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications is a Safety MCU IP core from Andes Technology Corp. listed on Semi IP Hub.

How should engineers evaluate this Safety MCU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Safety MCU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.