ARC Functional Safety Software

Today’s complex automotive applications require robust safety related hardware and software to meet the increasingly stringent au…

Overview

Today’s complex automotive applications require robust safety related hardware and software to meet the increasingly stringent automotive safety requirements defined by the ISO 26262 standard. This combination of safety mechanisms provides building blocks for the underlying safety infrastructure at the SoC level.

Many software components are required for customers to build their safety critical solutions. From a basic certified runtime library to a software test library necessary to achieve ASIL certification levels where redundant hardware is not present, to a set of components required to manage SoC level safety escalations, diagnostic error injection, test execution and fault detection time intervals (among other functions), Synopsys provides a comprehensive software offering.

The functional safety (FuSa) software components in conjunction with Synopsys’ ASIL certified MetaWare Development Tools for Safety and industry leading ARC® FS processors provide comprehensive ASIL compliant solutions which dramatically reduce customers’ risk and SoC certification effort.

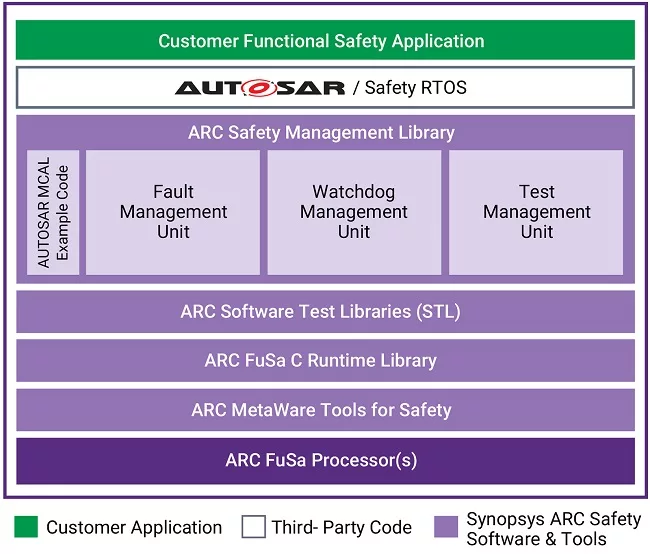

The FuSa software portfolio supports of a number of software components:

- Synopsys ARC Safety Management Library comprising test, fault, and watchdog manager units, example MCAL layer code and complex drivers to ease AUTOSAR integration

- Synopsys ARC Software Test Library (STL) implements an external software safety mechanism for ASIL certification where redundant hardware is not present

- Synopsys ARC FuSa C runtime library building blocks for safety-critical applications

Key features

Synopsys ARC Software Test Library (STL)

- ASIL-D certified software that implements external software-based hardware safety mechanism provided for EM22FS, HS4xFS, EV7xFS, VPX5FS processors

- Designed together with HW safety mechanisms to meet ASIL B requirements for non-lockstep cores with minimal extra HW and minimal SW overhead

- Made according to state-of-the-art SPFM proving process built with Synopsys EDA tools and matching ISO26262:2018 criteria

Synopsys ARC FuSa C-runtime library

- ASIL-D Certified subset of Standard C library suitable for safety critical applications including math.h functions, memory / string operations, character-handing operations, and ARC hardware-specific functions (interrupts, caches, timers, etc.)

- Freestanding subset of Standard C Library implementation according to ISO 9899:1999 Clause 4

- ARC-specific hardware abstraction layer

Synopsys ARC Safety Management Library

- Test Management Unit

- Plans and schedules test execution, and interacts with test providers to achieve full SoC test coverage

- Manages fault injection

- Works in boot and mission modes

- Fault Management Unit

- Collects, post-processes raw fault notifications from SoC components and converts into safety alarms

- Maintains severity, hierarchy, and aggregation of safety alarms

- Generates software visible safety alarms using callbacks or non-maskable interrupts

- Asserts hardware fault notification or reset signals

- Watchdog Management Unit

- Handles internal watchdogs to control program execution flow

- Handles external watchdog to guarantee system level fault detection time interval

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is ARC Functional Safety Software?

ARC Functional Safety Software is a CPU IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.