6MHz ±1% PVT 1.8V Low Power Oscillator in Silterra 0.18um

This macro-cell is a low-power, precision, general purpose 1.8V 6MHz ±1% PVT internal oscillator core aimed for clock generation.

Overview

This macro-cell is a low-power, precision, general purpose 1.8V 6MHz ±1% PVT internal oscillator core aimed for clock generation. A 7 bit digital bus allows frequency adjustment against process variations.

It features a self-biased, built-in references.

The core can be easily retargeted to any other frequencies between 1MHz and 30MHz and other CMOS technology that includes poly resistors.

Key features

- 6MHz +/- 1% after trimming

- Supply 1.8V +/- 10%

- Low power (17µA)

- Low TC (>175ppm/°C )

- 7-bit trimming

- Self-biased, built-in references

- Indicative area: 0.0165mm2

- Load capacitance: <100fF

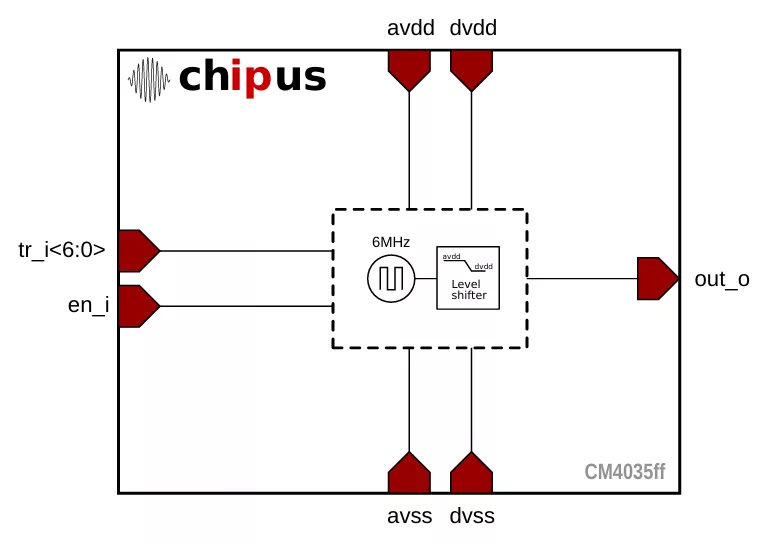

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| Silterra | 180nm | G | — |

Specifications

Identity

Provider

Learn more about Oscillator IP core

The Architectural Evolution of 16GHz PLLs for Next-Gen AI and SerDes SoCs

The Architectural Evolution of 16GHz PLLs for Next-Gen AI and SerDes SoCs

Creating a Frequency Plan for a System using a PLL

Introducing agileSecure anti-tamper security portfolio

Silicon-proven LVTS for 2nm: a new era of accuracy and integration in thermal monitoring

Frequently asked questions about Oscillator IP cores

What is 6MHz ±1% PVT 1.8V Low Power Oscillator in Silterra 0.18um?

6MHz ±1% PVT 1.8V Low Power Oscillator in Silterra 0.18um is a Oscillator IP core from Chipus Microelectronics listed on Semi IP Hub. It is listed with support for silterra.

How should engineers evaluate this Oscillator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Oscillator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.