12-bit Analog-to-Digital Converter

The agileADC 12 Analog-to-Digital Converter is a traditional Charge-Redistribution SAR ADC that is referenced to VDD, VSS.

Overview

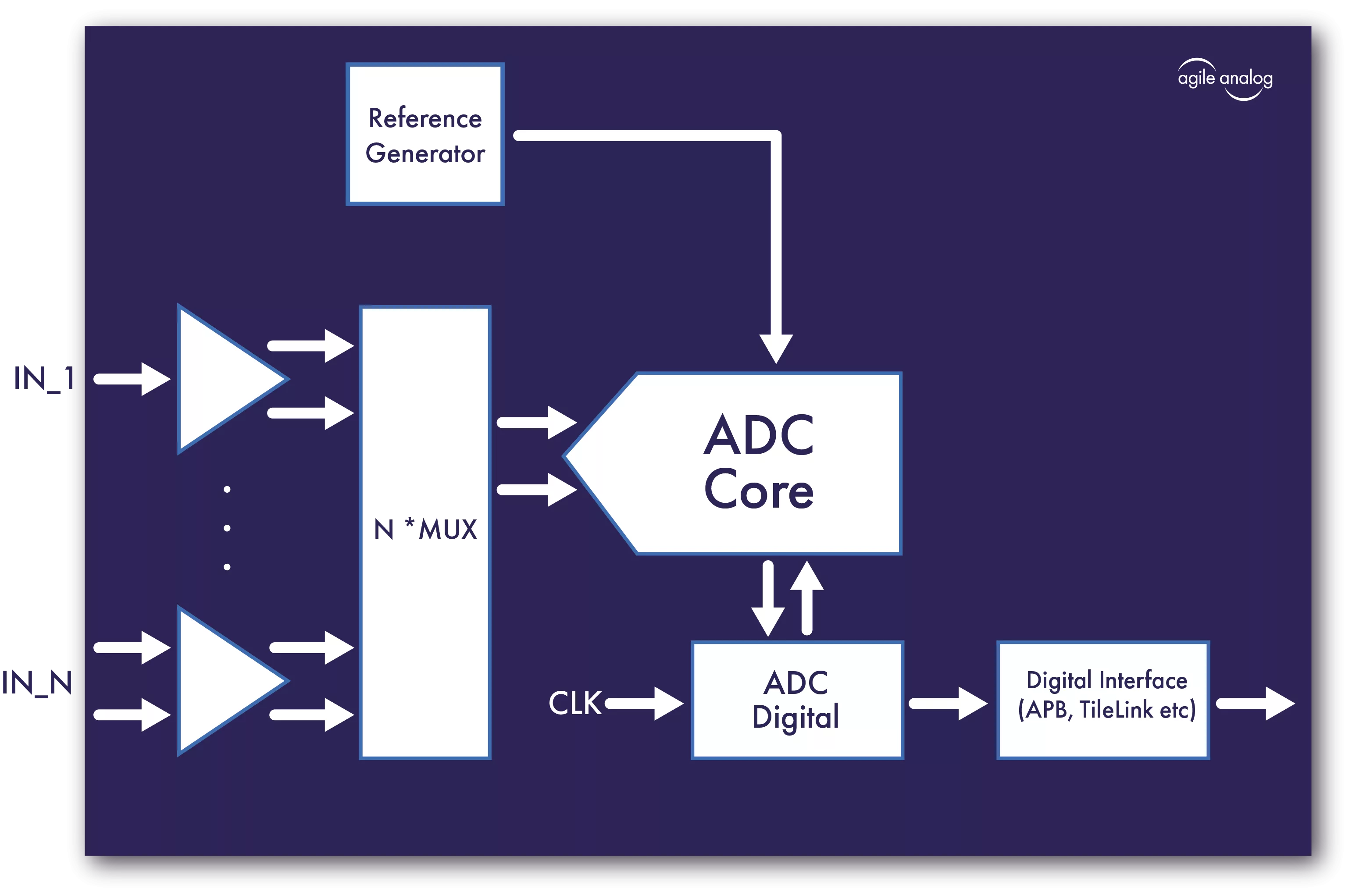

The agileADC 12 Analog-to-Digital Converter is a traditional Charge-Redistribution SAR ADC that is referenced to VDD, VSS. The architecture can achieve up to 12-bit resolution at sample rates up to 64 MSPS. It includes a 16-channel input multiplexor that can be configured to be buffered or unbuffered, and support differential or single-ended inputs.

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable leading to analog IP that is more verifiable, more robust and more reliable. Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Intel Foundry, Samsung Foundry, UMC and Other Foundries.

Key features

- Resolution: 12 bits

- Sampling Rate (Fs) 1: Up to 64 MSPS

- Input Signal Bandwidth: Fs/2

- SINAD1: Typ 69 dB

- ENOB1: Typ 11.3 bits

- SFDR1: Typ 90 dBc

- INL: +/2 LSB

- DNL: +/-1 LSB

- Monotonic and no missing codes

- Up to 16 input channels

- Integrated reference generator

- Integrated calibration mode

Block Diagram

Benefits

- Digitally Wrapped

- - AMBA-APB Interface to simplify integration, testing and operation.

- - Provided with System Verilog models

- DFT/DFM

- - Incorporated trim and calibration to facilitate process and/or manufacturing offsets to be adjusted

- - Built-in test mode

- Configurable Inputs

- - Up to 16 input channels

- - Buffer or unbuffered

- - Differential or Single-ended

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

What’s Included?

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Analog

Provider

Learn more about ADC IP core

Time Interleaving of Analog to Digital Converters: Calibration Techniques, Limitations & what to look in Time Interleaved ADC IP prior to licensing

Three ways of looking at a sigma-delta ADC device

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Save power in IoT SoCs by leveraging ADC characteristics

High Speed ADC Data Transfer

Frequently asked questions about ADC IP cores

What is 12-bit Analog-to-Digital Converter?

12-bit Analog-to-Digital Converter is a ADC IP core from Agile Analog listed on Semi IP Hub.

How should engineers evaluate this ADC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ADC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.