eSilicon宣布7nm 56G SerdS已经经过硅验证

Device defines a new level of flexibility, power and performance for 12.8 & 25.6Tb/s switches, routers and 400G systems

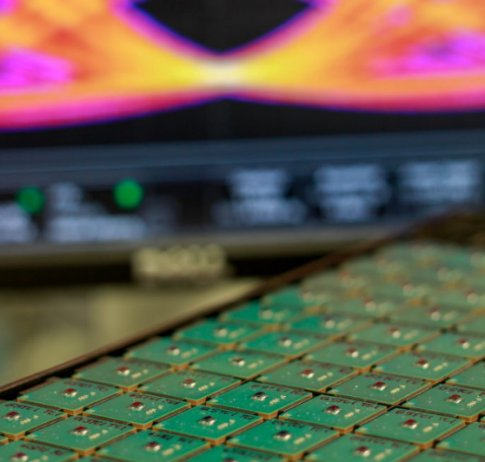

SAN JOSE, Calif. — September 13, 2018 — eSilicon, a leading provider of FinFET ASICs, market-specific IP platforms and advanced 2.5D packaging solutions, disclosed today that it has validated its 7nm 56G long-reach SerDes in silicon and that lab measurements confirm that the design is meeting or exceeding the target performance, power and functionality. Based on these results, eSilicon has begun to demonstrate its test chip to key customers.

“In the race to offer next-generation 7nm SerDes, the number of vendors offering silicon-proven designs is small,” said Mike Demler, senior analyst at The Linley Group and a senior editor at Microprocessor Report. “Demonstrating silicon performance for its 7nm device will help eSilicon establish itself in this high-end and strategic market.”

“eSilicon’s goal was to build a new-to-the-market SerDes that set a new standard for flexibility and performance,” said Hugh Durdan, vice president, strategy and products at eSilicon. “This first wave of measured silicon data proves we are hitting that mark. I look forward to additional proof points in the coming months.”

Key features of eSilicon’s 7n 56G long-reach SerDes include:

- High insertion loss tolerance with low bit error rates to support increased bandwidth in legacy equipment

- Support for Ethernet, OIF, Interlaken and Fibre Channel standards as well as customers’ proprietary rates

- The most flexible clocking architecture available with continuous operation from 1G-56G and independent Rx and Tx rates

- The lowest power available for this class of performance, easing system design and cooling constraints

- Easy integration, test and system bring-up with unprecedented levels of observability and controllability to maximize system performance and shorten time to market

The SerDes is part of eSilicon’s new 7nm plug & play IP platform for networking and switching applications. Parameters such as the control interface, DFT strategy, metal stack, operating range and reliability conditions are all compatible across IP in the platform. Configurability to facilitate optimized performance for the target application is also designed in. The result is shorter time to market with an optimized design.

To learn more about eSilicon’s 7nm plug & play IP platform or to schedule a demonstration of the 56G SerDes test chip, visit eSilicon’s SerDes web page or contact your eSilicon sales representative directly or via sales@esilicon.com.

About eSilicon

eSilicon provides complex FinFET ASICs, market-specific IP platforms and advanced 2.5D packaging solutions. Our ASIC-proven, differentiating IP includes highly configurable 7nm 56G/112G SerDes plus networking-optimized 16/14/7nm FinFET IP platforms featuring HBM2 PHY, TCAM, specialized memory compilers and I/O libraries. Our neuASIC™ platform provides AI-specific IP and a modular design methodology to create adaptable, highly efficient AI ASICs. eSilicon serves the high-bandwidth networking, high-performance computing, artificial intelligence (AI) and 5G infrastructure markets. www.esilicon.com

Related Semiconductor IP

- 1-56Gbps Serdes - 7nm (Multi-reference Clock)

- 1-56Gbps Serdes - 7nm (Ultra Low Latency)

- 1-112Gbps Serdes - 7nm

- 1-56Gbps Serdes - 7nm (PPA-optimized)

- 1-56Gbps Serdes - 7nm (Area-optimized)

Related News

- eSilicon 56G长距离7nm DSP SerDes现可授权

- 联发科技采用硅验证的7nm专用ASIC服务 发布全球首款完整的56G PAM4 SerDes

- ECOC 2019: eSilicon在7米及3米Samtec电缆组件上展示基于7nm 58G DSP的SerDes功能

- Credo在DesignCon展会上展示其56G PAM-4,56G NRZ和28G NRZ串行高速I/O (SerDes)技术