10mA 3.3V Low-Dropout (LDO) Regulator on XFAB XT018

The TS_VR_3V3_X8 is a 3.3V low-dropout linear regulator (LDO) to supply the digital core of an analog ASIC.

Overview

The TS_VR_3V3_X8 is a 3.3V low-dropout linear regulator (LDO) to supply the digital core of an analog ASIC. The LDO operates with an input voltage of 5V (supply voltage) and provides an output regulated voltage of 3.3V. The LDO can supply a maximum DC load current of 10mA.

OPERATING CONDITIONS

| Parameters | Values |

| Junction temperature range | 0°C to 80°C |

| Supply voltage VDD | 4.5V to 5.1V |

| Reference voltage VREF | 2.5V |

| External load capacitor | 70nF to 150nF |

| Load current ILOAD | 10mA max |

SPECIFICATION

| Parameters | Values |

| Regulated DC output voltage | 3.250V to 3.358V |

| Power Supply Rejection Ratio (PSRR) for f=<10MHz | 16.09dB min |

| Average supply current consumption (Excluding output current) | 140µA max |

| Startup time | 1.20ms max |

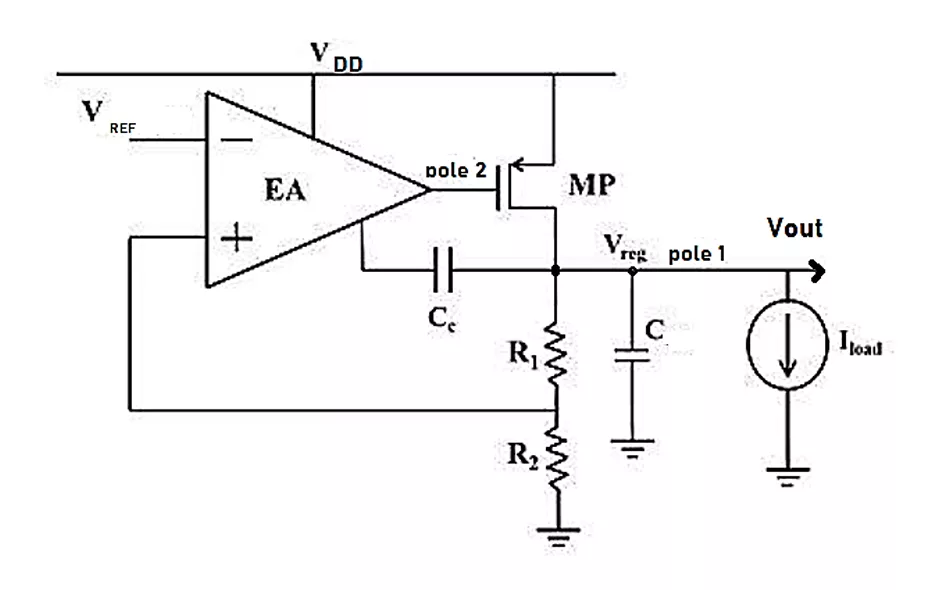

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about LDO Voltage Regulator IP core

Power Management for Internet of Things (IoT) System on a Chip (SoC) Development

Power management poses challenges

Tradeoffs of LDO Architectures and the Advantages of Advanced Architecture "Capless" LDOs

Key considerations and challenges when choosing LDOs

Introduction to Low Dropout (LDO) Linear Voltage Regulators

Frequently asked questions about LDO Voltage Regulator IP cores

What is 10mA 3.3V Low-Dropout (LDO) Regulator on XFAB XT018?

10mA 3.3V Low-Dropout (LDO) Regulator on XFAB XT018 is a LDO Voltage Regulator IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this LDO Voltage Regulator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LDO Voltage Regulator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.