Vendor:

T2M GmbH

Category:

USB

USB 3.0 Gen1 / Gen2 Host Controller IP

We provide configurable and scalable USB 3.1 host/device/dualmode controller IP Cores for a wide range of applications.

Overview

We provide highly configurable and scalable USB 3.1 host/device/dualmode controller IP Cores for a wide range of applications. The USB3.0 host controller is a highly integrated and cost-effective IP. It contains a USB3.0 PHY and a USB2.0 PHY. The USB3.0 PHY is used for Super-Speed (SS) transfers and the USB2.0 PHY is used for High-Speed (HS), Full-Speed (FS), and Low-Speed (LS) transfers. The USB 3.0 controller is designed for compliance with USB3.0 specification, Revision 1.0 and all associated ECNs, as well as USB specifications Rev 2.0 and associated ECNs. The USB 3.0 host controller based on xHCI specification, can be used in systems running any OS which provides xHCI/USB stacks, such as Android, Linux, or Windows. The USB 3.0 host controller exposes either an AXI or AHB master interface for the data path and an AHB slave interface for register access. Optionally, an interoperate proven third-party PCIe-AXI/AHB bridge can be provided for use in standard desktop/server applications.

Key features

- Compliant with XHCI Specification, Revision 1.0

- Compliant with USB 2.0 Specification, Revision 2.0

- Compliant with USB 3.0 Specification, Revision 1.0

- Supports DFT test for digital parts of the controller

- Supports Loopback test for USB2.0 PHY and USB3.0 PHY

- Compliant with USB 2.0 specification, Revision 2.0

- Supports High-Speed (480Mbps), Full-Speed (12Mbps) and Low-Speed (1.5Mbps) serial data rates

- Embedded 45ohm High-Speed termination, 1.5kohm Full-Speed device pull-up resistor, 15kohm pull-down resistors

- Embedded Phase-Locked Loop (PLL) for 480MHz High-Speed USB operations

- Embedded internal RREF for reference current trimming function

- Embedded HV protection circuit

- Provides one 5Gbps Super-Speed connection

- 270MHz differential CMOS reference clock

- 0.9V/1.8V supply rails

- On-chip 50? termination resistors

- 10-bit parallel interface (@ 500MHz)

- Programmable transmitter output swing and de-emphasis strength

- Configurable/adaptive equalizer to optimize receiver sensitivity

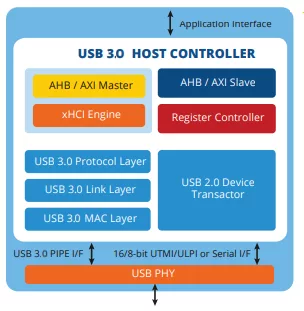

Block Diagram

USB 3.0 Host Controller IP block diagram

Benefits

- Highly modular and configurable design

- Layered architecture

- Fully synchronous design

- Support for both sync and async reset

- Clearly demarcated clock domains

- Extensive clock gating support

- Multiple power well support

- Software control for key features

Applications

- Desktop / Server Applications

- Automotive

- Smartphones

- Tablets

- Notebooks

- Gaming

- Digital cameras and camcorders

- Storage

- Wireless communication

- Set-top boxes

- Smart TVs and digital TVs

- Chip-to-chip low-power interconnects

What’s Included?

- Configurable RTL Code

- HDL-based test bench and behavioral models

- Test cases

- Protocol checkers, bus watchers, and performance monitors

- Configurable synthesis shell

- Design guide

- Verification guide

- Synthesis guide

- FPGA Platform for Pre-Tape-out Validation

Specifications

Identity

Part Number

USB 3.0 Host Controller IP

Vendor

T2M GmbH

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

T2M GmbH

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

In addition to performance and interoperability, achieving low power has been one of the requirements for industry standards specifications. Some of the key specifications like Universal Serial Bus (USB), PCI Express (PCIe), and MIPI have defined power saving features for burst traffic. This whitepaper explains how Synopsys USB IP offers low power using various low power states that go beyond the basic features.

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

Gervais Fong, Synopsys

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Sharmion Kerley, MIPI Alliance

Frequently asked questions about USB IP cores

What is USB 3.0 Gen1 / Gen2 Host Controller IP?

USB 3.0 Gen1 / Gen2 Host Controller IP is a USB IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.