SHA-384 and SHA-512 Secure Hash Crypto Engine

The SHA-384/512 is a high-throughput, and compact hardware implementation of the SHA-384 and the SHA-512 cryptographic hash funct…

Overview

The SHA-384/512 is a high-throughput, and compact hardware implementation of the SHA-384 and the SHA-512 cryptographic hash functions provisioned by the FIPS180-4 standard.

The core is designed for ease of use and integration and adheres to industry-best coding and verification practices. Technology mapping, and timing closure are trouble-free, as the core contains no multi-cycle or false paths, and uses only rising-edge-triggered D-type flip-flops, no tri-states, and a single-clock/reset domain. The SHA-384/512 core features a simple input and output data interface. Support for AMBA bus interfaces and integration with an external DMA are available as options.

The highly reliable SHA-384/512 has been production-proven in several ASIC and FPGAs designs.

Key features

- Custom-hardware accelerator for the SHA-384 and SHA-512 cryptographic hash functions

- Compliant to FIPS 180-4 with maximum message length up to (2128 – 1) bits

- High throughput:

- 81 clock-cycles per 1024-bit input block

- Throughput scaling with multiple clock instances.

- Small Silicon footprint: 15k-20k Gates

- Easy integration & implementation

- Fully synchronous, uses only the rising clock edge, single-clock domain, no false or multicycle timing paths, scan-ready, LINT-clean, reusable design

- Simple input and output interfaces optionally bridged to AMBA™ interfaces or integrated with a DMA engine.

- Available in VHDL or Verilog source code format, or as a targeted netlist for AMD/Xilinx, Intel FPGA, Lattice, Microsemi, or other FPGA devices

- Complete deliverables include test benches, C model, and test vector generator

- Multiple times production-proven in ASIC and FPGA designs

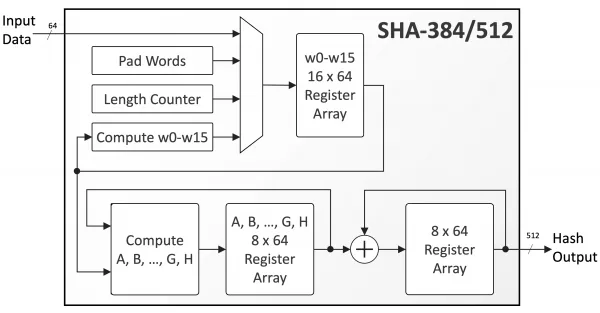

Block Diagram

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Hash / MAC IP core

Embedded Security explained: Cryptographic Hash Functions

Embracing a More Secure Era with TLS 1.3

Standardized PUF-based Solution for Device eID

Implementing Ultra Low Latency Data Center Services with Programmable Logic

Security in vehicular systems

Frequently asked questions about Hash / MAC IP cores

What is SHA-384 and SHA-512 Secure Hash Crypto Engine?

SHA-384 and SHA-512 Secure Hash Crypto Engine is a Hash / MAC IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Hash / MAC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Hash / MAC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.