SATA Verification IP

SATA Verification IP provides an smart way to verify the SATA bi-directional bus.

Overview

SATA Verification IP provides an smart way to verify the SATA bi-directional bus. The SmartDV's SATA Verification IP is fully compliant with revision 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5 of the SATA Specification and provides the following features.

SATA Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SATA Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Supports 1.5, 3 and 6 Gbps speeds.

- Supports Port Multiplier Discovery and Enumeration.

- Supports following interfaces

- 1 bit

- 8 bit

- 10 bit

- 20 bit

- 32 bit

- 40 bit

- 64 bit

- Disparity checking.

- Kcode & Dcode validity and alignment.

- 8b/10b Encode and Decode functions.

- Controls to inject bit errors.

- OOB sequence generation and checking.

- Digital SERDES model included.

- Callbacks for use in directed test writing.

- Selectable as Host or Device BFM.

- Complete Link Layer state machine.

- Selectable Primitive CONT and fill substitution processing.

- Selectable data scrambling option.

- Configurable Receive and Transmit fifo latencies.

- 8b/10b encoding and decoding, Error injection.

- Configurable OOB signals and speed of operation.

- Configurable phy layer timers.

- User defined primitive transmission.

- Single or multi-bit error injection.

- User defined primitives & frame transmission.

- Supports link layer power modes.

- SYNC injection during FIS transfer.

- Randomized/directed CRC error injection and checking.

- Ability to enable/disable scrambling on the fly.

- Programmable enable/disable & duration of DMAT, CONT and HOLD primitives.

- Callback functions for state transitions, primitive and FIS reception/transmission

- OOB transmission/reception and speed change.

- Supports LBA with HDD size configuration.

- APIs providing backdoor access to HDD.

- Programmable auto-activate support using configuration.

- Supports all standard ATA command sets including NCQ.

- Configurable FIS latencies, FIFO depths and FIS size.

- Supports PIPE interface.

- Supports 8,16,32,64 bit SERDES interface.

- Supports Asynchronous notification.

- Supports Asynchronous Signal Recovery.

- Supports Speed Switching/Negotiation.

- Set Features support.

- Device Configuration Overlay.

- Software Settings Preservation and Hardware Feature Control support.

- Supports Staggered Spin up.

- Supports the Non 512 Byte Sector Size.

- Support for Enclosure Management/Services is available.

- Supports HDD activity activation.

- Ability to Automatic Partial to Slumber Transitions.

- Supports DHU Specific Operation.

- Rebuild Assist is supported.

- Supports Intermixing of Non-native queued commands with Native Queued commands.

- Enabled Hybrid Information Feature.

- Device Signature return Feature.

- Supports SATA Logs.

- Optional DC-IDLE pin

- Supports FPDMA Zone management commands.

- Supports Queued version of ACS-4 Zero EXT command.

- Supports Receive FPDMA Queued to support ZAC.

- Supports Data Set Management aligned with ACS-4 and Data Set Management XL command.

- Supports ZAC Management Logs for NCQ Non data and Send/Receive FPDMA commands.

- Supports Out of band management control structures

- Callbacks in Host, Device and monitor for user processing of data.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- SATA Verification IP comes with complete testsuite to test every feature of SATA specification.

- Functional coverage for complete SATA features.

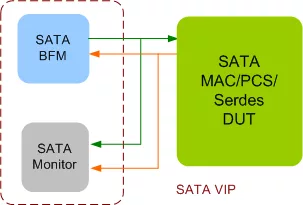

Block Diagram

Benefits

- Faster testbench development and more complete verification of SATA designs.

- Easy to use command interface simplifies testbench control and configuration of Host and Device.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SATA testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SATA Controller IP core

Verification of USB 3.0 Device IP Core in Multi-Layer SystemC Verification Environment

Designing Around an Encrypted Netlist: Is The Pain Worth the Gain?

STBus complex interconnect design and verification for a HDTV SoC

Interface IP: Winners, Losers in 2013

The IP Paradox: Sales are growing despite Semi Consolidation

Frequently asked questions about SATA Controller IP

What is SATA Verification IP?

SATA Verification IP is a SATA Controller IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SATA Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SATA Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.