Power on Reset with detector

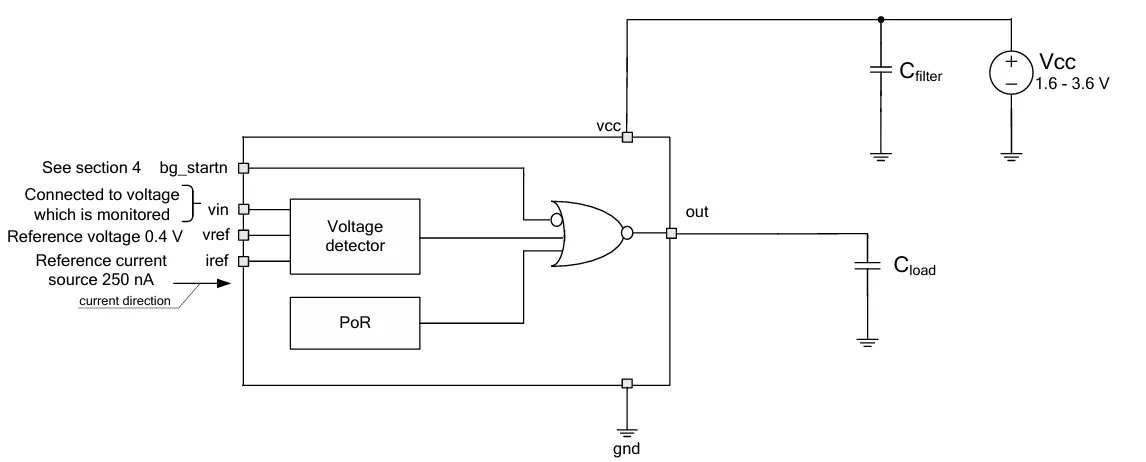

The block consists of voltage detector, power on reset and NOR3 gate.

Overview

The block consists of voltage detector, power on reset and NOR3 gate.

The voltage detector is a comparator that compares input voltage with reference voltages.

The power on reset is a special circuit that generates a signal after rising supply voltage required for the initial state of the triggers.

The block is designed on Global Foundries CMOS 55nm technology.

Key features

- Global Foundries CMOS 55nm

- Low current consumption

- Small area

Block Diagram

Applications

- Power on reset

- Supply voltage level detector

What’s Included?

- Schematic or NetList

- Abstract view (.lef and .lib files)

- Layout (optional)

- Behavioral model (for functional verification)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 55nm | 55 550 nm | Silicon Proven |

Specifications

Identity

Provider

Learn more about Power On Reset (POR) IP core

Analysis of RDC Paths for a million gate SoC

The silicon enigma: Bridging the gap between simulation and silicon

BIST Verification at SoC level

Reusable Verification Infrastructure for A Processor Platform to deliver fast SOC development

High Density - Low power Flip-Flop

Frequently asked questions about Power-On Reset (POR) IP cores

What is Power on Reset with detector?

Power on Reset with detector is a Power On Reset (POR) IP core from NTLab listed on Semi IP Hub. It is listed with support for globalfoundries Silicon Proven.

How should engineers evaluate this Power On Reset (POR)?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Power On Reset (POR) IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.