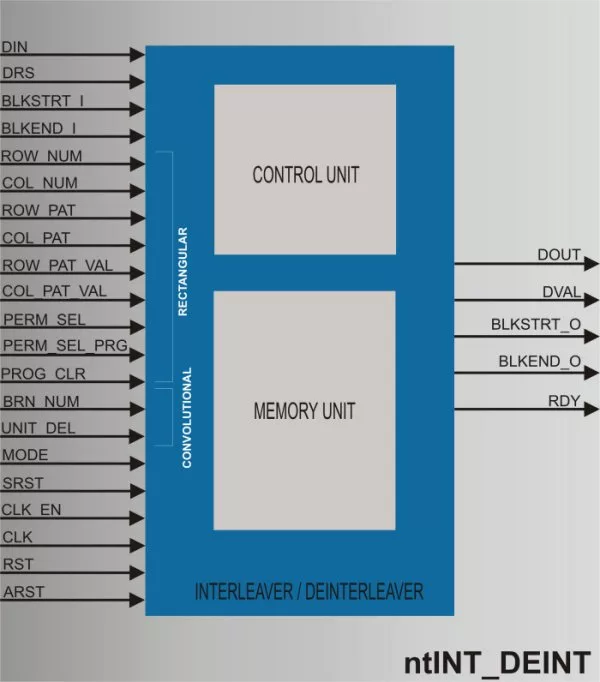

Interleaver / De-interleaver

Configurable interleaving/deinterleaving function that can be used in a wide range of applications that employ channel coding.

Overview

Configurable interleaving/deinterleaving function that can be used in a wide range of applications that employ channel coding.

Key features

- Support for block or convolutional (de interleaving algorithm.

- Programmable interleaving or deinterleaving functionality.

- Parameterized symbol width and codeword length.

- Programmable block size, number or rows/columns.

- Programmable rows/columns permutations.

- Programmable number of branches and branch length.

- Compatible with continuous or burst mode Reed Solomon codecs.

- Fully synchronous design using a single clock.

Block Diagram

What’s Included?

- Synthesizable VHDL or Verilog code.

- Comprehensive test bench.

- Detailed user's guide.

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 180nm | BCDG2 | Silicon Proven |

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is Interleaver / De-interleaver?

Interleaver / De-interleaver is a Channel Coding IP core from Noesis Technologies listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.