I/O Library with LVDS in SkyWater 90nm

Standard GPIO, I2C-compatible ODIO, analog I/O, and integrated LVDS for robust mixed-signal and moderate-speed differential interfaces

Overview

A SkyWater I/O Library combining standard GPIO, I2C-compatible ODIO, analog I/O, and integrated LVDS for robust mixed-signal and moderate-speed differential interfaces.

The Certus S90 Mixed-Signal I/O Library is a silicon-proven I/O platform for the SkyWater 90nm process, supporting single-ended digital I/O, ODIO, analog pads, and an integrated 3.3V LVDS macro. The library enables flexible pad-ring construction using inline or dual-staggered cells and is optimized for reliable operation across wide voltage and temperature ranges. Integrated LVDS supports point-to-point differential links up to 1.16 Gbps without the complexity or power overhead of a full SerDes solution.

Operating Conditions

| Parameter | Value |

| Core VDD | 1.2V |

| I/O | 1.8V-3.3V |

| BEOL | 1P5M |

| LVDS | 3.3V |

| Tj | -40C to 125C |

| ESD | 2kV HBM, 500V CDM |

| Latch-up | Immune |

Cell Size and Metal Stack

| Cell Type | Config. |

| Pad Size | 50um x 50um |

| I/O Cell (Inline) | 70um x 130um |

| I/O Cell (Dual) | 35um x 130um |

Key features

LVDS Features

- Data rate validated to 1.16Gbps

- Typical Differential Swing: 330mV

- Typical Common-mode voltage: 1.25V

- Controlled rise/fall times: 150ps, 5pf load

- Integrated amplitude control

GPIO & ODIO Features

- 1.8V-3.3V GPIO operation

- Push-pull GPIO with tri-state output

- Programmable drive strength and slew rate

- Input hysteresis / Schmitt-trigger inputs

- I2C-compatible ODIO operation

- Failsafe behavior when VDDIO is off

- Inline and dual-staggered pad-ring compatible

- Deep N-well / triple-well friendly

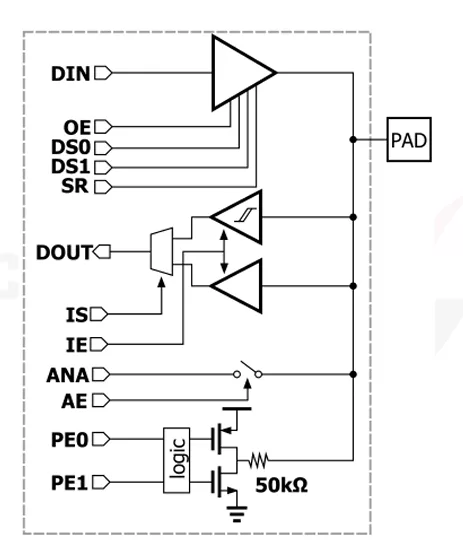

Block Diagram

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| SkyWater | 90nm | S90 | — |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about High-Speed IP core

PCIe 5.0: The universal high-speed interconnect for High Bandwidth and Low Latency Applications Design Challenges & Solutions

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

Driving the Future of High-Speed Computing with PCIe 7.0 Innovation

High-Speed Test IO: Addressing High-Performance Data Transmission And Testing Needs For HPC & AI

eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

Frequently asked questions about High-Speed I/O Pad IP

What is I/O Library with LVDS in SkyWater 90nm?

I/O Library with LVDS in SkyWater 90nm is a High-Speed IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for skywater.

How should engineers evaluate this High-Speed?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this High-Speed IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.