Overview

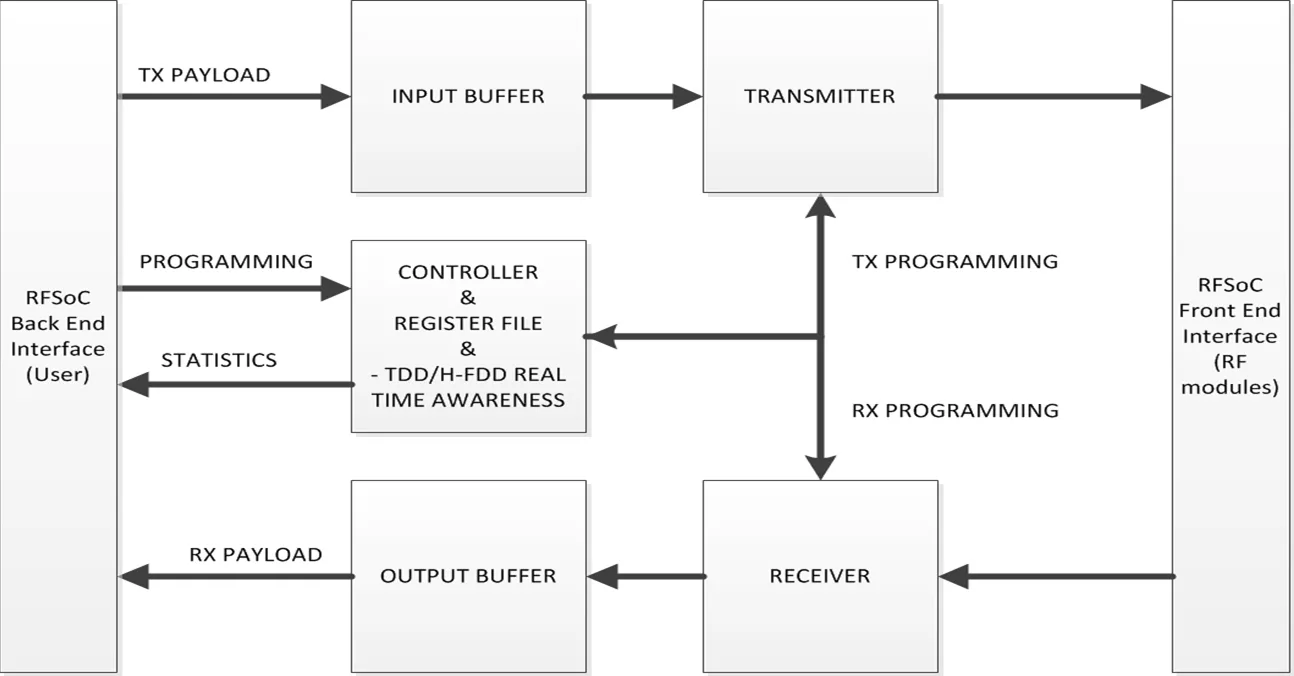

The ntOFDM_HS_BBP IP implements the physical layer transmission and reception processing engines of a custom subset of the 802.16-2012 standard. The ntOFDM_HS_BBP IP core main functional blocks are the Transmitter, the Receiver, the Register File and High Level Controller and the Analog Front End interface. The User programs the Register file in order to define the systems functionality, configure control parameters, and define the desired modes of operation. The Analog Front End interface module connects the ntOFDM_HS_BBP produced sample rate to the any AFE board with all the appropriate rate conversions.

The Transmitter includes the Bit Level Processing Block (BLPB) and the Symbol Level Processing Block (SLPB). The BLPB operates on Users/Bursts payload bytes and uses Scrambling, FEC encoding, Interleaving and Symbol Modulation to produce I/Q modulated symbols. The SLPB operates on the produced symbols and uses them to generate the OFMDA-Symbol stream, inserts pilots and guard intervals, transforms the signal to the time domain (FFT transform) and adds the Cyclic Prefix.

The Receiver includes the Synchronizer, the SLPB and the BLPB main processing blocks. The Synchronizer searches for a known pattern (Preamble) in an effort to detect the exact start of a new incoming frame. It applies STO and CFO corrections on the signal. The SLPB operates on the synchronized signal and tries to compensate the channel impairments applied on the signal, while bringing it back to the frequency domain. It also demodulates the OFMDA symbols back to data symbols and provides them to the BLPB. The BLPB RX implements the exact op-posite procedure to the BLPB TX and recovers the corrected Users/Bursts payload bytes.

A real-time demonstration video of ntOFDM_HS_BBP IP Core can be downloaded from

http://www.noesis-tech.com/downloads/OFDM_Demo.mp4

Learn more about Cellular IP core

Chet Babla, ARM

By Hantro

SATCOM is adopting 3GPP 5G NTN standards to scale beyond proprietary silos, enabling interoperable satellite networks and global direct‑to‑cell services.

Ceva’s 2025 Technology Symposium series, held in Shanghai, Hsinchu and Herzliya , brought together a global community of engineers, product leaders, and ecosystem partners. Each location had its own flavor, but a single theme ran through every discussion: how to bring meaningful intelligence to the edge of every device.