DVB-S2X LDPC/BCH Decoder

The DVB-S2X decoder is a silicon-proven, scalable solution that allows for symbol rates of up to 100 MSymbols/s on FPGAs.

Overview

The DVB-S2X decoder is a silicon-proven, scalable solution that allows for symbol rates of up to 100 MSymbols/s on state-of-the-art FPGAs. DVB-S2X is the next generation satellite transmission standard which is an extended version of its well-established predecessor DVB-S2. The new specification allows for spectral efficiency gains of up to 50% by offering lower roll-off factors, higher modulations and a finer code rate granularity compared to DVB-S2.

Key features

- Compliant with DVB-S2 and DVB-S2X

- Support for decoding of BBFRAMEs

- Support for ACM, CCM, and VCM

- Support for very low SNR modes (VLSNR) with SNRs below -9 dB

- Support for short, medium, and normal frames (16,200 bits, 32,400 and 64,800 bits)

- Support for BPSK, QPSK, 8-PSK, 16-APSK, 32-APSK, 64-APSK, 128-APSK, and 256-APSK

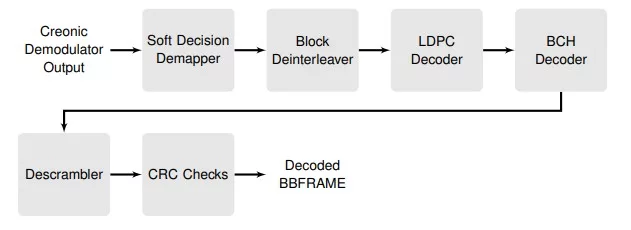

Block Diagram

Benefits

- Validated against 3rd party DVB-S2X modulators

- Silicon-proven IP core

- Based on industry-proven design for DVB-S2

- Soft-Decision demapper, block deinterleaver, LDPC decoder, BCH decoder, descrambler, and CRC checks included

- Low-power and low-complexity design

- Frame-to-frame on-the-fly configuration

- Design-time configuration of throughput for optimal resource utilization

- Faster convergence due to layered LDPC decoder architecture

- Early stopping criterion for iterative LDPC decoder, saving a considerable amount of energy

- Configurable amount of LDPC decoding iterations for trading-off throughput and error correction performance with on-the-fly selection in ACM/VCM modes

- Collection of statistics (error rates, average number of iterations, signal-to noise ratio (SNR))

- Available for ASIC and FPGAs (AMD Xilinx, Intel, Microchip)

- Deliverable includes VHDL source code or synthesized netlist, HDL simulation models, VHDL or SystemC testbench, and bit-accurate Matlab, C or C++ simulation model

Applications

- Satellite communication

- Applications with the highest demands on forward error correction

- Applications with the need for a wide range of code rates (1/10 to 9/10)

What’s Included?

- VHDL source code or netlist

- HDL simulation models

- VHDL or SystemC testbench

- Bit-accurate Matlab, C or C++ simulation model

- Comprehensive documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is DVB-S2X LDPC/BCH Decoder?

DVB-S2X LDPC/BCH Decoder is a Channel Coding IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.