Digital Video Overlay Module

VID_OVERLAY is a versatile video multiplexer that allows one video stream to be inserted over another.

Overview

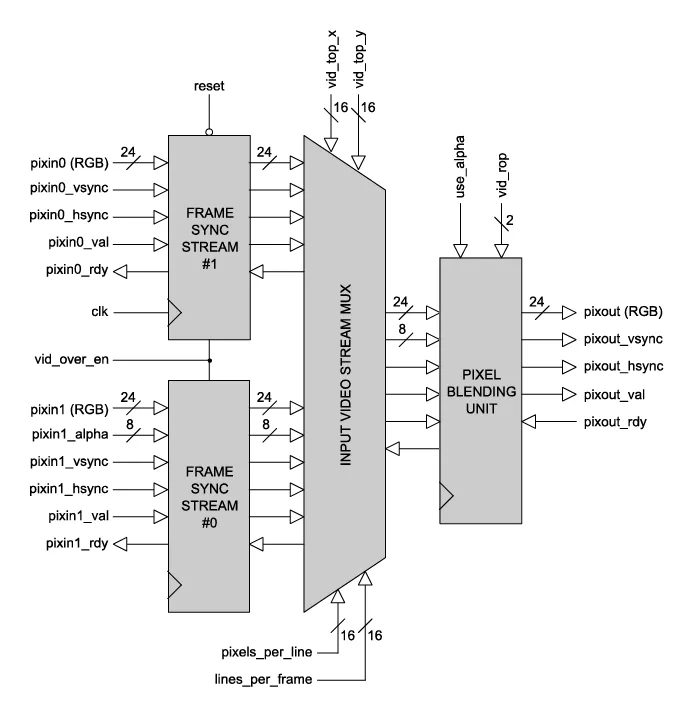

VID_OVERLAY is a highly versatile video multiplexer that allows one video stream to be inserted over another. By cascading a series of video overlay modules together, any number of video sources may be multiplexed together. The module supports input video streams of any resolution or aspect ratio up to 216 x 216 pixels in size. Video overlay parameters may be changed on a frame-by-frame basis to dynamically change the size and position of the video overlay.

Pixels and syncs flow in and out of the video overlay module in accordance with the valid-ready pipeline protocol. Pixels and syncs are sampled at the module inputs on a rising clock-edge when 'val' is high and 'rdy' is high. Likewise, pixels and syncs are transferred out of the module on a rising clock-edge when 'val' is high and 'rdy' is high. The pipeline protocol allows both input and output interfaces to be stalled independently.

The dimensions of the output video are controlled entirely by the background video stream (pixin0) . This means that if the source video input at stream '0' is 1024x768 pixels then the output video will also be 1024x768 pixels in resolution. The video overlay enters the module via stream '1' and must be smaller or equal in size to the background video stream.

In addition, the overlay module supports a number of blending operations including an 8-bit alpha channel and bitwise AND, OR and XOR functions. Figure 1 shows the architecture of the digital video overlay module in more detail

Key features

- Synthesizable, technology independent VHDL IP Core

- Video overlays on 24-bit RGB or YCbCr 4:4:4 video

- Supports all video resolutions up to 216 x 216 pixels

- Supports any number of input video streams or video overlays (by cascading modules together in series)

- Programmable video-overlay position and size

- Per pixel 8-bit alpha transparency

- Choice of ROP commands including AND, OR and XOR

- Simple input and output interfaces

- No complex programming required

- Easily integrates with all Zipcores Video IP

- Small implementation size

- Supports FPGA clock rates in excess of 250 MHz

Block Diagram

Applications

- Digital TV and home-media solutions

- Broadcast TV and film production

- Digital-video special effects

- Multiple video windows

- Animated video windows

- Picture-in-Picture (PiP) applications

- Instrumentation and monitoring

- Network and Tactical operations centres

- CCTV and security camera systems

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Digital Video Overlay Module?

Digital Video Overlay Module is a Video Processing IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.