Secure Hash Algorithm 256 IP Core

A universal solution that effectively accelerates the SHA2-256 hash function conforming with FIPS PUB 180-4 is the SHA2-256 bridg…

Overview

A universal solution that effectively accelerates the SHA2-256 hash function conforming with FIPS PUB 180-4 is the SHA2-256 bridge to APB, AHB, and AXI bus. It has two modes for computing message digests: 256-bit and 224-bit. A message length of up to 264 +/- 1 bit may be entered. It also natively supports the SHA2-256 HMAC (Keyed-Hash Message Authentication Code), a cryptographic function defined in RFC 2104. This depends on the core settings. This IP is appropriate for secure communication in general as well as for verifying data integrity and authenticity in digital signature methods. It may also be applied to speed up calculations related to cryptocurrencies.

Key features

- FIPS PUB 180-4 compliant SHA2-256 function

- RFC 2104 compliant HMAC mode native support

- SHA2 224 and 256 bit modes support

- Secure storage for precomputed HMAC keys

- Hash/HMAC context swapping

- Internal, automatic padding module

- Binary message resolution support

- Flexible data read/write modes

- Software driver with OpenSSL/MbedTLS interface ready

- Available system interface wrappers:

- AMBA – APB / AHB / AXI Bus

- Altera Avalon Bus

- Xilinx OPB Bus

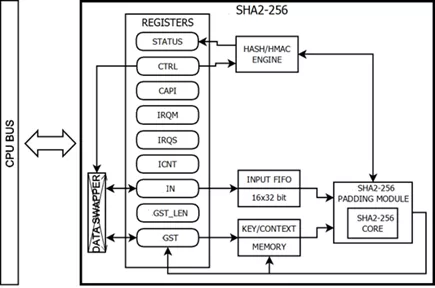

Block Diagram

Applications

- Digital signature

- Data integrity

- Key derivation

- TLS/SSH/PGP IPsec communication

What’s Included?

- Source code:

- VERILOG test bench environment

- Technical documentation

- Synthesis scripts

- Example application

- Technical support

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Hash / MAC IP core

Embedded Security explained: Cryptographic Hash Functions

Embracing a More Secure Era with TLS 1.3

Standardized PUF-based Solution for Device eID

Implementing Ultra Low Latency Data Center Services with Programmable Logic

Security in vehicular systems

Frequently asked questions about Hash / MAC IP cores

What is Secure Hash Algorithm 256 IP Core?

Secure Hash Algorithm 256 IP Core is a Hash / MAC IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this Hash / MAC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Hash / MAC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.