Customizable Display Controller IP

CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant para…

Overview

CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output. Several features can be configured at synthesis time and programmed at run time. The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

The main functionality of CDC is reading images (layers) from memory, combining them on-the-fly e.g. by blending, cropping and windowing and generating a pixel output stream of the combined image. The CDC supports image composition as well as partial screen updates.

On the output the controller provides a digital RGB signal (or optionally a digital component YCbCr signal) with video data and signals for horizontal/vertical blank and synchronization. The output interface is compliant with the MIPI-DPI standard and can be easily connected with any video output controller like HDMI, MIPI-DSI, 3G-SDI or a Video DAC. Optionally, the composed image can be written back to memory.

CDC Configurability

Based on a highly modular architecture the CDC-Family offers a wide range of features from CDC-200 providing basic functionality with each family member offering additional configurable feature extensions up to the flag-ship CDC-500 which supports output image rotation. The features are configurable at design-time and can be controlled at run-time via an simple basic driver for register agnostic control or a Khronos standard OpenWF Display API driver.

The following table outlines the set of configurable features for all CDC-Family members:

| Feature | CDC-200 | CDC-300 | CDC-400 | CDC-500 |

|---|---|---|---|---|

| Layer Blending | x | x | x | x |

| Windowing | x | x | x | x |

| Gamma Correction | x | x | x | x |

| Color Keying | x | x | x | x |

| Dithering | x | x | x | x |

| Layer CLUT | x | x | x | x |

| RGB/Greyscale Input Formats | x | x | x | x |

| RGB888 Output | x | x | x | x |

| Mirroring (H & V) | x | x | x | x |

| Dual View | x | x | x | |

| Scaling | x | x | x | |

| YCBCR Input Formats | x | x | x | |

| YCBCR Output Formats | x | x | ||

| Programmable Layer Blending Order | x | x | ||

| Missed-Pixel Handling | x | x | ||

| Single Frame Mode | x | x | ||

| Dual CPU Support | x | x | ||

| Frame CRC | x | x | ||

| Rotation | x | |||

| Composition Capture | x |

Application Example

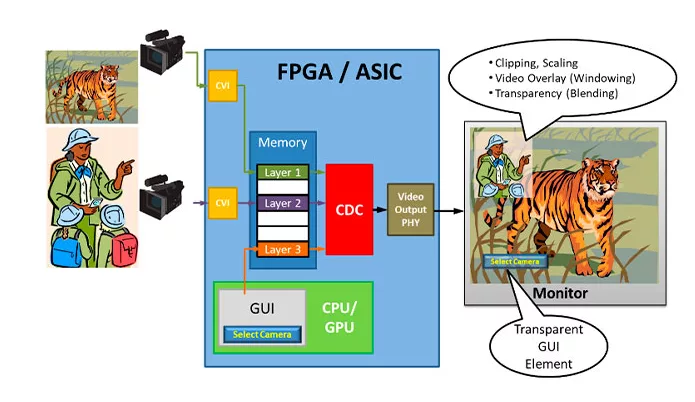

In this example, images from two video cameras are transferred to frame buffers in memory using two CVIs (Configurable Video Input controller, another TES IP), while the internal CPU/GPU generates GUI elements to be used in the displayed image in a 3rd framebuffer. The CDC clips and scales the image stored in layer 2 and blends it with the main image on layer 1, using windowing to display it in the upper left corner, while adding some transparency to keep the occupied part of the main image visible. The GUI element is blended into the lower left corner, again using the transparency feature of the CDC.

The resulting image is transferred as RGB888 pixel stream to a Video PHY block, which provides a standard video display interface (e.g. MIPI, DVI, HDMI, ...) suitable for the attached monitor.

Key features

- Layer Blending

- Windowing

- Gamma Correction

- Color Keying

- Dithering

- Layer CLUT

- RGB/Greyscale Input Formats

- RGB888 Output

- Dual View

- Scaling

- Mirroring (H & V)

- YCBCR Input Formats

- YCBCR Output Formats

- Layer Blending Order

- Missed-Pixel Handling

- Single Frame Mode

- Dual CPU Support

- Frame CRC

- On the fly 90° or 270° rotation

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Display Controller IP core

Empowering AI-Enabled Systems with MIPI C/D-PHY Combo IP: The Complete Audio-Visual Subsystem and AI

High Speed, Low Power and Flexibility Drive DisplayPort's Increasing Popularity

The whys and hows of secure boot

Motion Picture: a Reality on Emulation Platform

Sequential clock gating maximizes power savings at IP level

Frequently asked questions about Display Controller IP

What is Customizable Display Controller IP?

Customizable Display Controller IP is a Display Controller IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this Display Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Display Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.