ChaCha20 DPA Resistant Crypto Accelerator

Rambus DPA Resistant Hardware Cores prevent against the leakage of secret cryptographic key material through attacks when integra…

Overview

Rambus DPA Resistant Hardware Cores prevent against the leakage of secret cryptographic key material through attacks when integrated into an SoC or FPGA. ChaCha 20 Fast DPA resistant cryptographic accelerator core.

The DPA Resistant Hardware cores offer chipmakers an easy-to-integrate technology-independent soft-macro security solution with built-in side-channel resistance for cryptographic functions across a wide array of devices.

These high-performance cores provide a higher level of protection than standard security cores, while improving time-to-market, as all the cores are validated DPA countermeasures. It is highly flexible for integration with standard cipher modes such as Cipher Block Chaining (CBC), Counter (CTR) and Authenticated Encryption mode / Galois Counter (GCM) modes. The fast AES core performs AES encryption with DPA protection using only 2 clock cycles per AES round, outperforming any existing solution.

Key features

- Quicken time-to-market using precertified DPA Countermeasures

- Highly secure cryptographic engine primitives

- Extensive validation using the Test Vector Leakage Assessment (TVLA) methodology (revealing no leakage beyond 100 million traces)

- Cores protected against univariate first- and second-order side-channel attacks beyond 1 billion operations

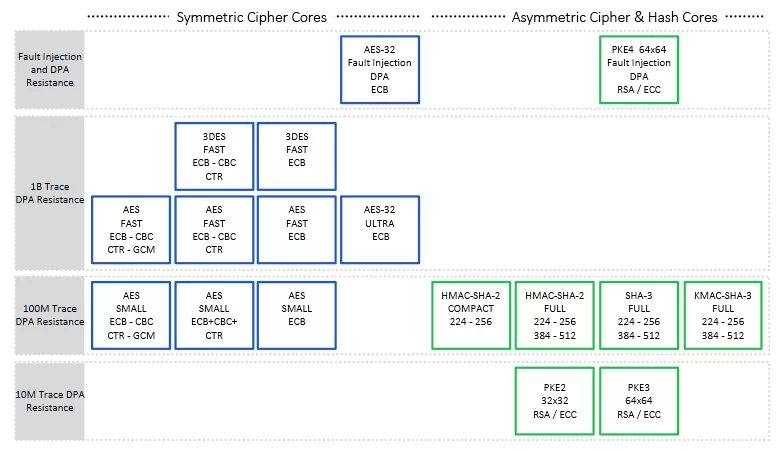

- DPARC cores are available for AES (128/256), 3DES, SHA-2 (224/256 or 224/256/384/512), HMAC-SHA-2 (224/256 or 224/256/384/512), RSA, ECDSA, and ECDH

- Implements silicon proven and validated DPA countermeasures such as LMDPL (LUT-Masked Dual-rail with Pre-charge Logic) gate-level masking

- Simple control/status interface

- No routing constraints required

- Delivers highest level of security with side-channel resistance prioritized

- Also available as non-protected standard versions.

Block Diagram

Benefits

- Side channel attack resistant

- Technology and node independent

- Superior cryptographic protection

- Use with any ASIC or FPGA

Applications

- Government, Automotive, Military, Edge, IoT, Machine Learning (ML), Artifical Intelligence (AI), Semiconductor, Processors, Cryptocurrency

What’s Included?

- Configurable Cryptographic Core: Verilog RTL reference design

- Synthesis Inputs: SDC constraint file suitable for FPGA or ASIC synthesis

- Full Documentation: Specification documents and Integration guides

- Functional Testbench: NIST-compliant test vectors

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Symmetric Crypto IP core

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Google, Quantum Attacks, and ECDSA: Why There’s No Need to Panic and Why Preparation Matters Now

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Frequently asked questions about Symmetric Cryptography IP cores

What is ChaCha20 DPA Resistant Crypto Accelerator?

ChaCha20 DPA Resistant Crypto Accelerator is a Symmetric Crypto IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.