Bilinear Video Scaling Engine

XY2_SCALER is a very high quality video scaler capable of generating interpolated output images from 16x16 up to 216 x 216 pixels…

Overview

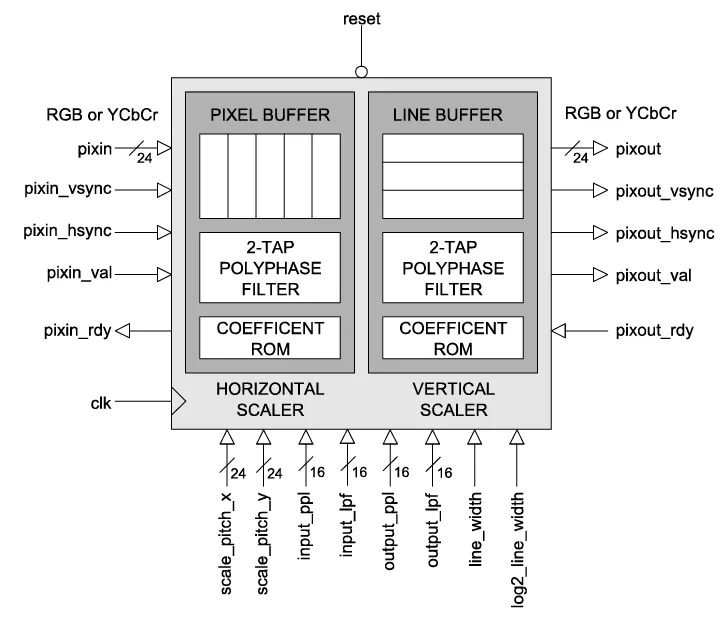

XY2_SCALER is a very high quality video scaler capable of generating interpolated output images from 16x16 up to 216 x 216 pixels in resolution. The architecture permits seamless scaling (either up or down) depending on the chosen scale factor. Internally, the scaler uses a 24-bit accumulator and a bank of polyphase FIR filters with 16 phases or interpolation points. All filter coefficients are programmable, allowing the user to define a wide range of filter characteristics.

Pixels flow in and out of the scaling engine in accordance with the valid ready pipeline protocol. Pixels are transferred into the scaler on a rising clock-edge when pixin_val is high and pixin_rdy is high. Likewise, pixels are transferred out of the scaler on a rising clock-edge when pixout_val is high and pixout_rdy is high. As such, the pipeline protocol allows both input and output interfaces to be stalled independently.

Key features

- Synthesizable, technology independent VHDL IP Core

- Versatile 24-bit RGB/YCbCr video scaler capable of scaling up or down by any factor. Different pixel formats supported on request

- 24-bit accumulator with 24-bit scale-pitch in [24 12] format

- Supports all video resolutions between 16x16 and 216x 216 pixels

- Fully pipelined architecture with simple flow control

- Features a 2x2 polyphase filter in the x and y dimensions. Each filter has 16 unique phases or interpolation points

- Fully programmable filter coefficients to suit the desired application

- Example bilinear coefficients shipped with the design

- Output rate is 1 x 24-bit pixel per clock for scaling factors > 1

- Generates one scaled output frame for every input frame

- No frame buffer required

- Supports 250MHz+ operation on basic FPGA devices

Block Diagram

Benefits

Applications

- High quality 24-bit RGB/YCbCr video scaling

- Conversion of popular video formats to any other resolution such as VGA to XGA, SVGA to HD1080 etc.

- Digital TV set-top boxes and home media solutions

- Conversion to non-standard video resolutions - e.g. for use in portable devices and flat-panel displays

- Dynamic scaling of video in a window on a frame-by-frame basis

- Picture in Picture (PiP) applications

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Bilinear Video Scaling Engine?

Bilinear Video Scaling Engine is a Video Processing IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.