DAC 2024 - Showcasing the future of RISC-V through EDA

Brett Cline, Codasip

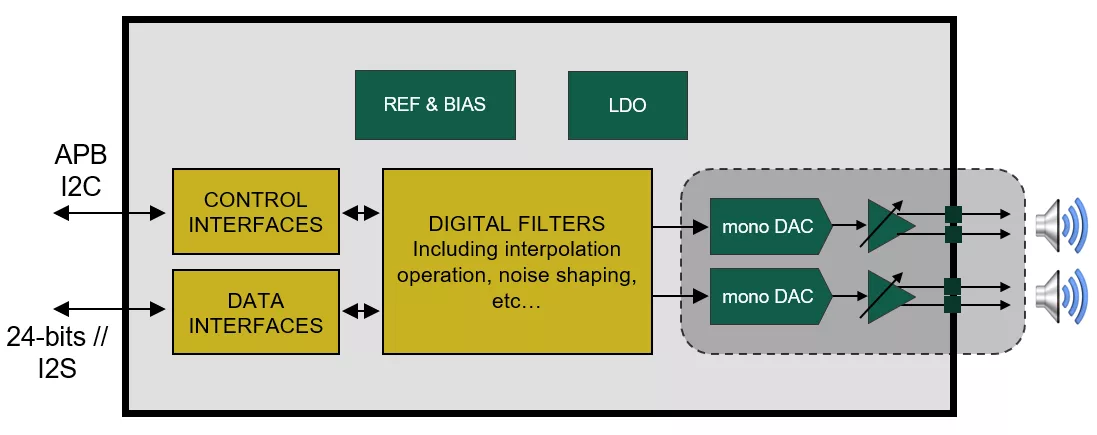

The sDAC-uLP-SW3-LR.01 is a mixed (analog and digital) Virtual Component containing a stereo DAC, and additional functions offeri…

Note: some files may require an NDA depending on provider policy.

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 22nm | ULL | Pre-Silicon |

24-bit cap-less Audio DAC 120dB SNR low latency is a DAC IP core from Dolphin Semiconductor listed on Semi IP Hub. It is listed with support for tsmc Pre-Silicon.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DAC IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.