1Kbyte EEPROM with configuration 64p8w16bit

180SMIC_EEPROM_08 is a nonvolatile electrically erasable programmable read-only memory (EEPROM) with volume 1 Kbyte (16(bit per w…

Overview

180SMIC_EEPROM_08 is a nonvolatile electrically erasable programmable read-only memory (EEPROM)

with volume 1 Kbyte (16(bit per word) x 8(words per page) x 64(pages)) with single-bit output data and parallel write data in one word.

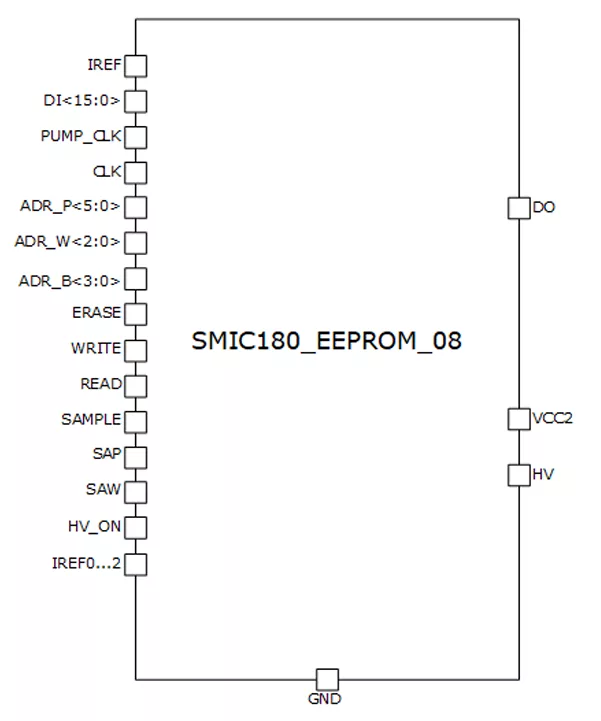

Write EEPROM page data comes to input DI<15:0> and write process execute if signal WRITE = “1”.

Data DI<15:0>, page address ADR_P <5:0>, word address in page ADR_W <2:0> cannot be changed until the end of the writing process. Data reading is carried out by specifying the page address ADR_P <5:0> and the address of the word in the page ADR_W <2:0>, as well as the reading bit in the word ADR_B <3:0>. After applying the reading strobe, the DO signal is set at the output corresponding to the reading data from the corresponding addresses of the EEPROM cell. Memory is optimized for usage in the industrial and commercial applications, requiring low power consumption and supply voltage.

Key features

- SMIC EEPROM CMOS 0.18 um

- High density of memory cells

- Writing and erasing data by one high-voltage pulse

- Programming and erase time – 2 ms (determined by specification of the EEPROM SMIC cell)

- Data retention over 10 years (endurance 105 cycles, determined by SMIC technology)

- Low power dissipation in standby and active mode

- Internally organized 16(bit per word) x 8(word per page) x 64(page) bit

Block Diagram

Applications

- Access control systems

- Radio-frequency identification systems, smart cards

- Electronic devices with battery power

- Chip serial ID and chip safety

- Electronic tags UHF band

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| SMIC | 180nm | G | Silicon Proven |

Specifications

Identity

Provider

Learn more about EEPROM IP core

Understanding Physical Unclonable Function (PUF)

Types of Storages for Computing System-On-Chips

SRAM PUF - The secure silicon fingerprint

CSoC Platform / Digital Subsystem IP for IoT

The future of the 8051 legacy upgraded for the Internet of Things (IoT)

Frequently asked questions about EEPROM IP cores

What is 1Kbyte EEPROM with configuration 64p8w16bit?

1Kbyte EEPROM with configuration 64p8w16bit is a EEPROM IP core from NTLab listed on Semi IP Hub. It is listed with support for smic Silicon Proven.

How should engineers evaluate this EEPROM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this EEPROM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.