1.8V/3.3V I/O Library with 5V ODIO & Analog in TSMC 16nm

A Flipchip I/O Library with dynamitcally switchable 1.8V/3.3V GPIO, 5V I2C/SM- Bus ODIO, 5V OTP Cell, 1.8V & 3.3V Analog Cells an…

Overview

A Flipchip I/O Library with dynamitcally switchable 1.8V/3.3V GPIO, 5V I2C/SM- Bus ODIO, 5V OTP Cell, 1.8V & 3.3V Analog Cells and associated ESD.

A key attribute of this library is its ability to detect and dynamically adjust to a VDDIO supply of 1.8V or 3.3V during system operation. The GPIO cell can be configured as input, output, open-source, or open-drain with an optional internal 50K ohm pull-up or pull-down resistor. Four selectable drive strengths are offered (25-235MHz @1.8V,10pF)to optimize across SSO currents & power. The output driver exhibits 50 (ś20%) termination across PVT to reduce reflections at higher operating frequencies. Supply cells for VDDIO, VREF, and core VDD include necessary built-in ESD circuitry. A 5V I2C / SMBUS open-drain (fail-safe) cell, 5V OTP programming gate cell and 1.8V & 3.3V analog cells with ESD protection are included. The library features protection break cells to allow for separate grounds while maintaining ESD robustness. ESD design targets are 2KV HBM, & 500VCDM,yet this libraryhas consistently demonstrated 4KV HBM. This library can also support 2KV IEC 61000-4-2 system ESD with appropriate integration.

Operating Conditions

| Parameter | Value |

| VDDIO | 1.8V/3.3V Selectable |

| VREF | 1.8V |

| Core | 0.8V |

| BEOL | 1P8M or 1P10M |

| Cell Size | 30x50um |

| Temperature | -40C to 125C |

| Max Load | 50pF (1opF at speed) |

Library Cell Summary

| Cell Type | Feature |

| GPIO | 25-235MHz, selectable |

| I2C ODIO | 5V, fail-safe |

| Analog | 1.8V & 3.3V |

| Supply/ESD | 1.8V/3.3V; 1.8V; 0.8V; GND |

| OTP | 5V progamming gate cell |

| Break Cells | VDDIO, VDD, VSS |

Key features

- Multi-voltage 1.8V/3.V switchable operation

- 4 selectable drive strengths

- Full-speed output enable

- Independent power sequencing

- 50(ś20%) source termination across PVT

- Schmitt Trigger Receiver

- 50K selectable pull-up or pull-down resistor

- ESD: 2kV HBM, 500V CDM, 2KV IEC61000-4-2

- Silicon Proven

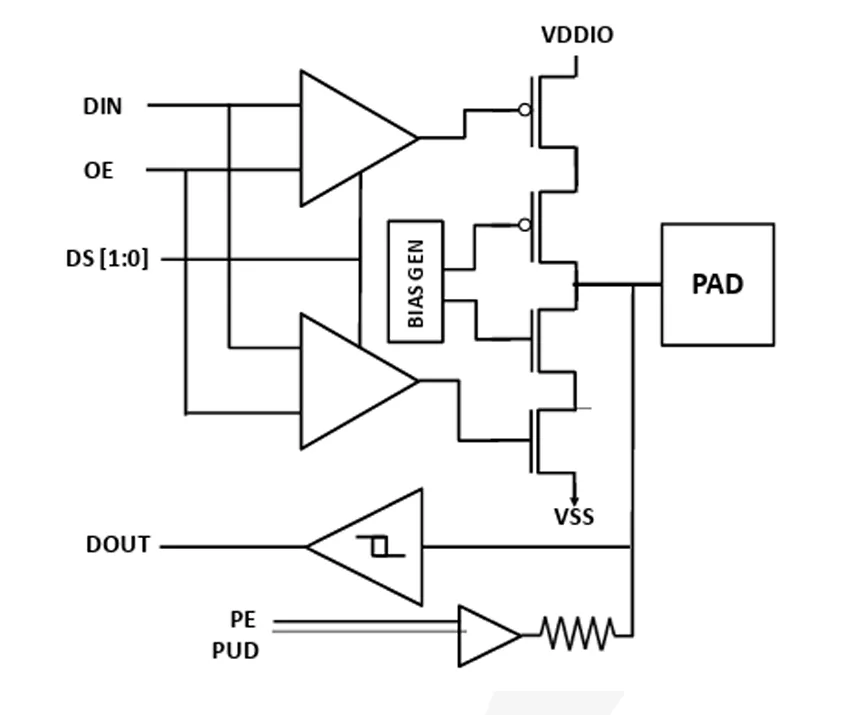

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 16nm | 16nm 160 nm | — |

Specifications

Identity

Provider

Learn more about Analog IP core

Analog Foundation Models

AnaFlow: Agentic LLM-based Workflow for Reasoning-Driven Explainable and Sample-Efficient Analog Circuit Sizing

Why Anti-tamper Sensors Matter: Agile Analog and Rambus Deliver Comprehensive Security Solution

Introducing agileSecure anti-tamper security portfolio

The Hidden Threat in Analog IC Migration: Why Electromigration rules can make or break your next tapeout

Frequently asked questions about Analog I/O Pad Library IP cores

What is 1.8V/3.3V I/O Library with 5V ODIO & Analog in TSMC 16nm?

1.8V/3.3V I/O Library with 5V ODIO & Analog in TSMC 16nm is a Analog IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Analog?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Analog IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.